一种用于超高速ADC的输入信号缓冲器设计

作者 胡远冰 电子科技大学 微电子与固体电子学院(四川 成都 610054)

本文引用地址:https://www.eepw.com.cn/article/201805/380762.htm胡远冰(1989-),男,硕士生,研究方向:模拟集成电路设计。

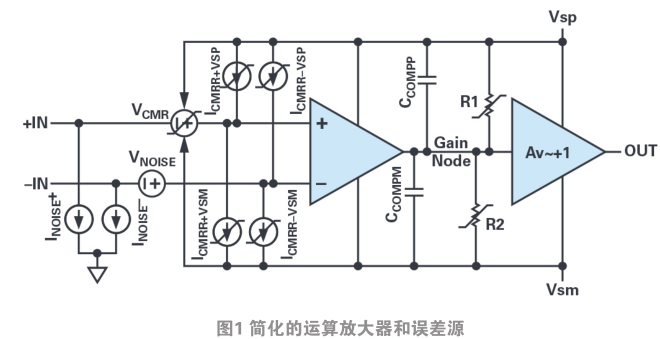

摘要:提出一种基于TSMC40LP工艺的输入信号缓冲器,用于12 bit 4 GSPS ADC的缓冲器设计。本缓冲器采用开环源随器结构,由于工艺角和温度变化,开环结构的缓冲器的输出共模将会漂移,导致比较器的输入共模发生漂移,使得比较器的比较结果发生错误。采用Replica共模反馈的方式为主缓冲器提供共模,实现缓冲器的输出共模的稳定,避免比较器因为共模变化而工作不正常。为了达到线性度的要求,通过叠层源随器和电容,将输入信号耦合到源随器的漏端,避免了短沟道器件的沟调效应。源随器采用深N阱器件,消除了衬底偏置效应。本源随器提供强大的输入信号驱动,避免多通道ADC交织时,相互之间的影响。同时驱动大的电容负载,并提供高质量的输入信号。后仿真得到源随器的最小带宽为9.7 GHz,在1 pF负载,500 MHz,800 mVpp输入信号时,SFDR为79.86 dB,满足12 bit 4 GSPS ADC的要求。

0 引言

输入信号缓冲器,可以采用闭环单位增益运放的方式实现,这也是最为常见的方式。对于低速ADC而言,可以不用缓冲器,或者闭环运放的方式,而超高速ADC而言,如果不采用缓冲器,通常封装的寄生电感会使得输入信号质量变差。高速高带宽应用的闭环运放稳定性是很难保证的。缓冲器将提供强大的输入信号驱动,避免多通道ADC交织时,相互之间的影响。同时驱动大的电容负载,并提供高质量的输入信号。因此对于超高速ADC而言,输入信号缓冲器是至关重要的模块之一。源随器作为ADC的缓冲器,其输出阻抗低,结合ADC的采样电容,可以达到宽带的目的。

1 硬件设计

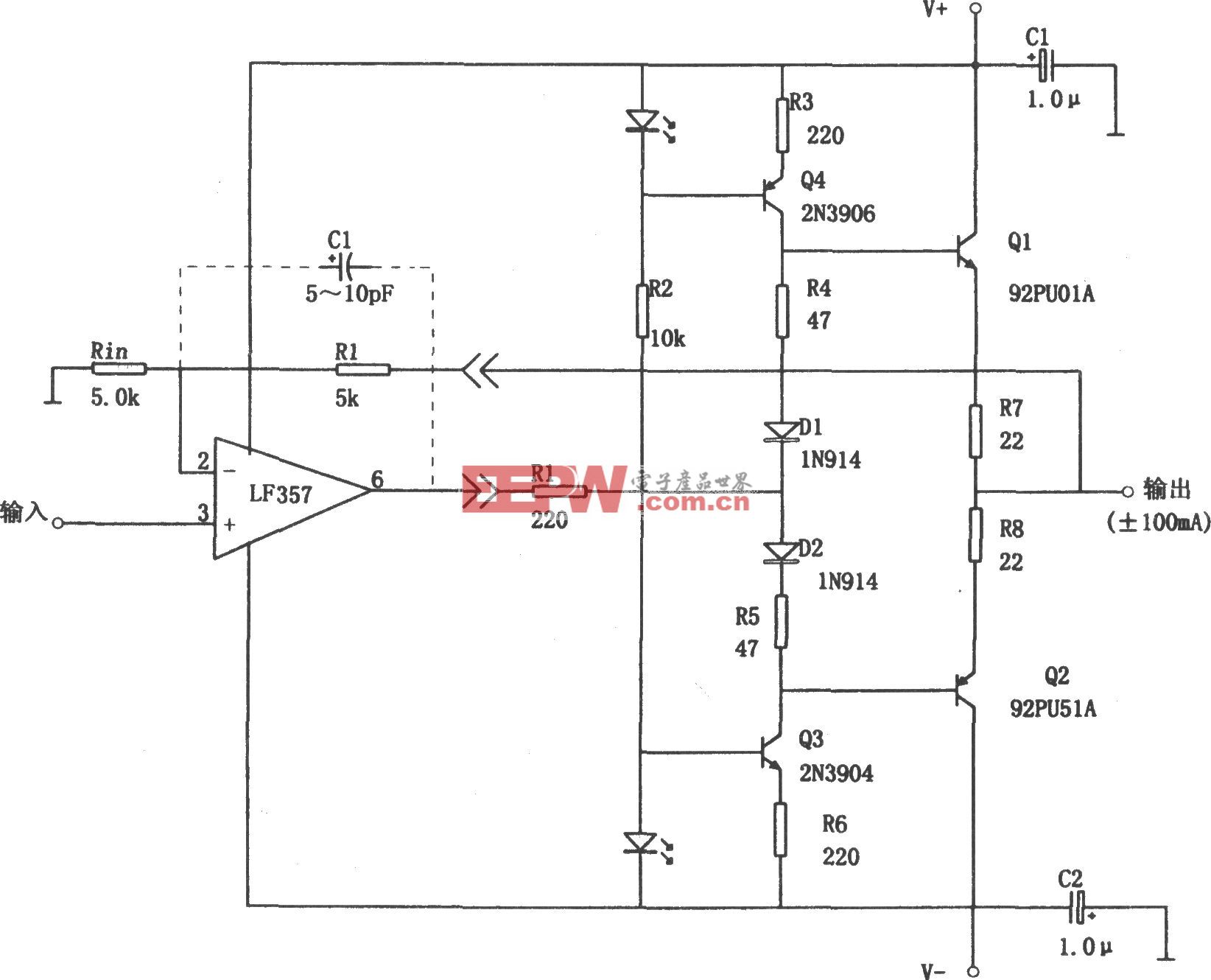

常见的源随器主要有两种结构:单管源随器[1](Source follower)和超级源随器[2](Super-source follower)。

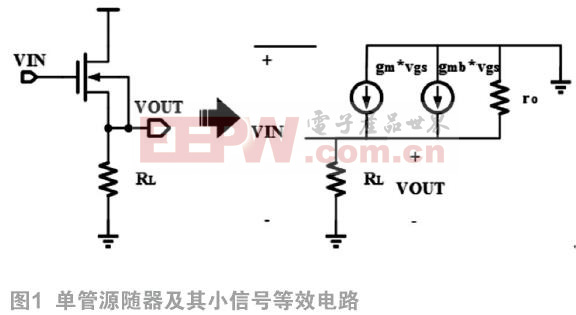

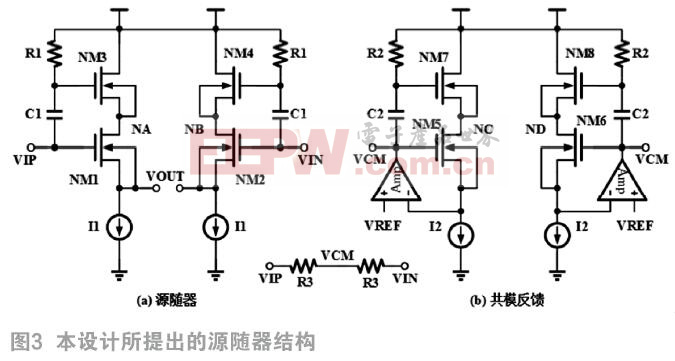

图1为单管源随器电路及其小信号等效电路,通过小信号等效模型可以计算出输入输出增益和输出阻抗。从其表达式也可以看出,输入输出增益近似为单位增益,输出阻抗小,但是输入输出的线性度受沟道调制效应、衬偏效应(深N阱工艺不受影响)的影响,使得输入输出线性度在高频时迅速变差。

(1)

(1)

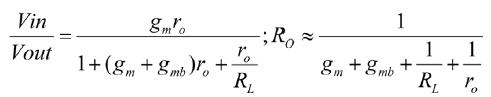

由于MOS管的跨导较小,单管源随器的输出阻抗较大,要实现大带宽较为困难,需要较大的功耗。为了进一步减小输出阻抗,采用负反馈方式的超级源随器,以输出阻抗减小环路增益的倍数。超级源随器及其小信号等效电路[2],如图2所示。

当输入信号保持不变时,输出减小,使得NM1的漏端也减小,PM1的栅源电压增大,流过PM1的电流变大,使得输出电压增大,实现电压负反馈,达到稳定输出的目的。根据KCL方程可以得到超级源随器的增益和输出阻抗的表达式:其中rno与rpo分别为NM1与PM1的输出阻抗;r1与r2为电流源的输出电阻。

(2)

(2)

假设电流源是理想电流源,与单管源随器相比具有更大的增益,更小的输出阻抗。但是超级源随器仍然存在沟调效应和衬偏效应非理想因素的影响,导致高频输出信号的线性度变差。调研发现,有不少的文章都在致力于解决上述源随器存在的非理想效应[3-6],但是效果不是很理想,不能应用于超高速ADC。

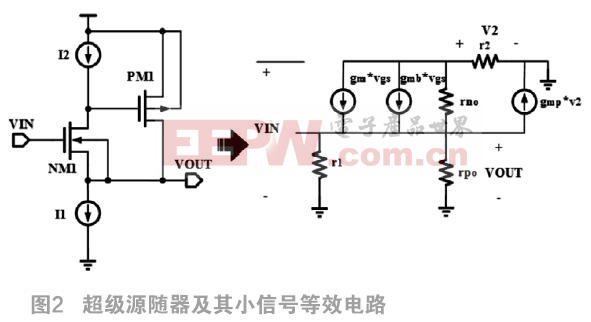

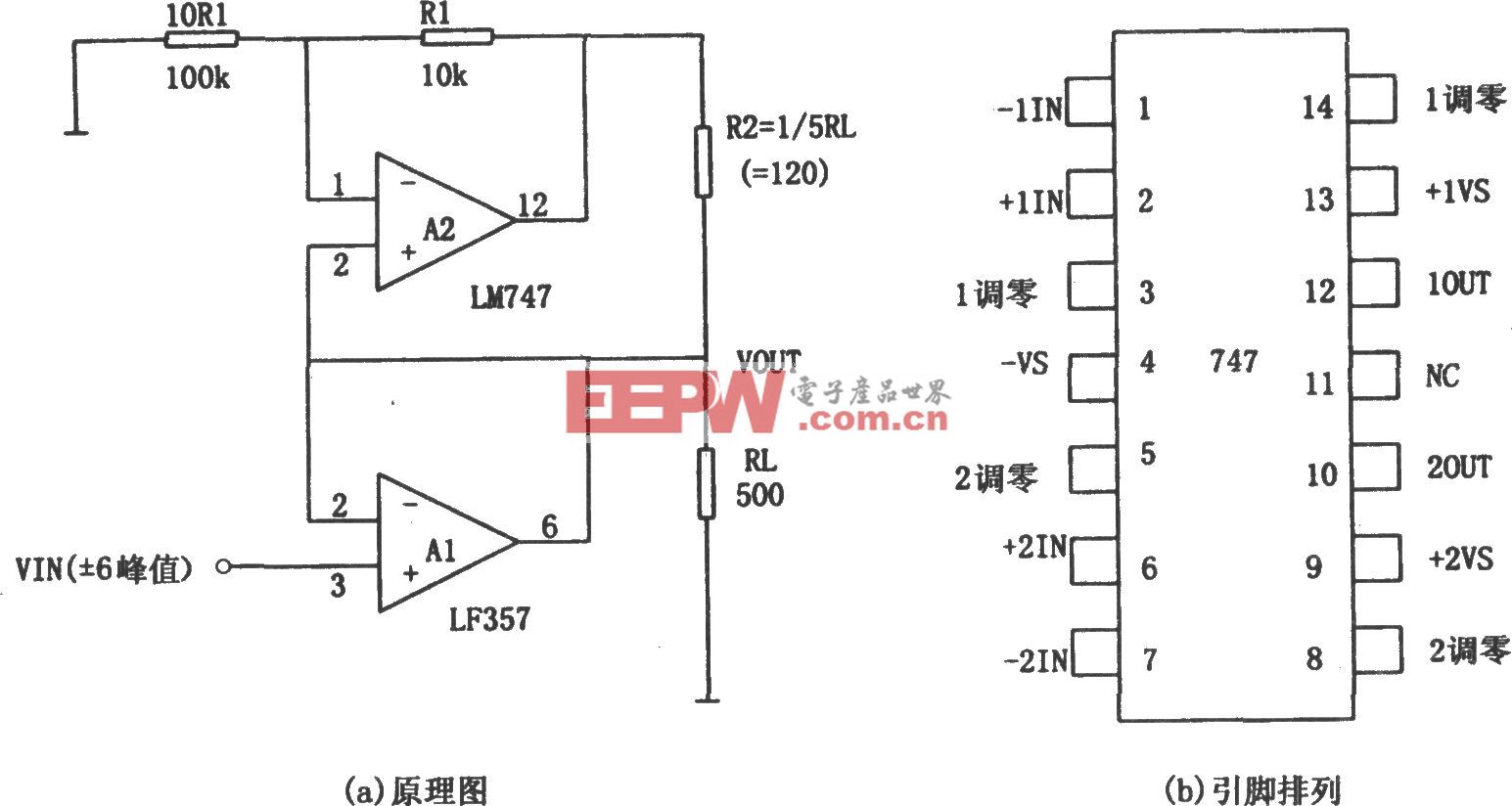

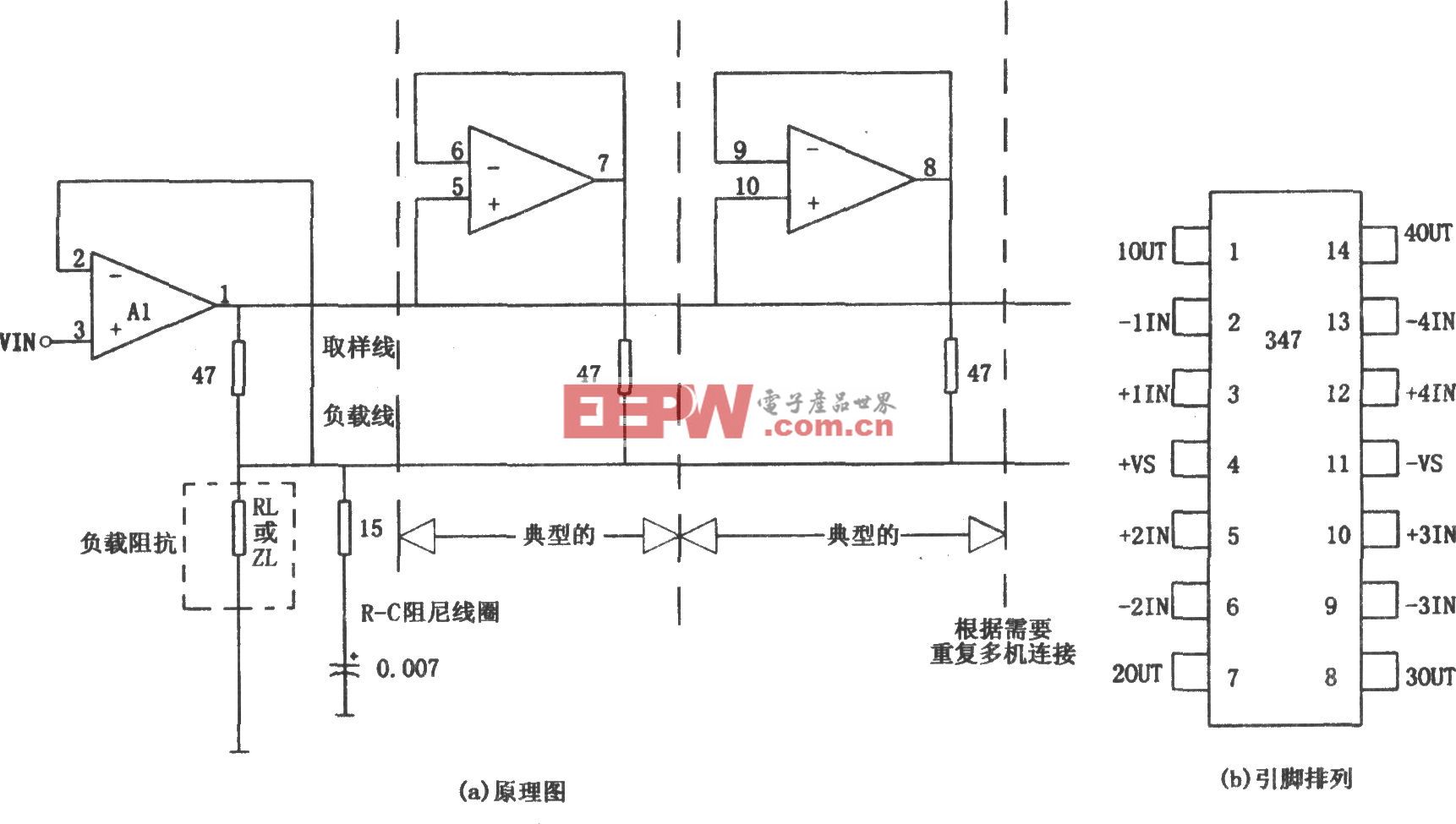

通过上述的分析,传统的源随器与超级源随器结构均存在沟道调制效应和衬底偏置效应,会影响高速ADC输入信号的线性度,恶化ADC的性能[7]。基于调研分析,采用一种解决沟道调制效应和衬底偏置效应的源随器结构[3-4],同时能够满足超高速ADC的线性度要求。图3为本设计采用的适用于超高速ADC输入信号缓冲器的基本电路结构。NM1、NM2、NM3、NM4构成源随器的主要输入对管。R1、C1解决高频输入时的源随器线性度下降。R3为终端电阻,其共模电压由共模反馈部分提供。NM5、NM6、NM7、NM8和Amp构成共模反馈。

本设计所采用的源随器电路解决了传统源随器存在的非理想因素。NM1、NM2、NM3、NM4均为深N阱器件,在设计时不用考虑衬底偏置效应的影响。通过C1、NM3、NM4将输入信号耦合到节点NA、NB,使得NM1、NM2的漏源电压变化减小,减小了沟调效应的影响,提高线性度。传统的设计是不含共模反馈的,对于超高速ADC应用的缓冲器设计共模反馈需要很高的带宽,在稳定性方面是很难保证的,而且功耗非常大。为了克服输出输共模随温度和工艺的变化,提出了共模反馈的解决方案,为了满足超高速ADC的应用,本设计提出了Replica的共模反馈方式,给主源随器提供共模电压,将源随器按比例复制用于共模反馈,那么共模反馈部分工作在DC状态,稳定性可以很好地得到满足,功耗也较低。通过共模反馈的使用,解决了因为工艺角和温度变化使得输出共模变化的问题,保证后续比较器能够正常工作。

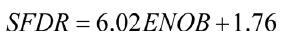

在设计源随器时,根据ADC的指标来计算,对于12 bit 4 GSPS ADC而言,用SFDR近似SNDR计算:

(3)

(3)

要达到12位精度,SFDR=74 dB,要达到11位精度,SFDR=67.98 dB。

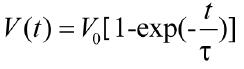

对于输入buffer,以单极点近似有:

(4)

(4)

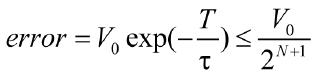

要求在一个周期内buffer的输出能够建立到0.5 LSB范围内:

(5)

(5)

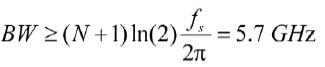

得到输入buffer的带宽满足:

(6)

(6)

考虑工艺角和温度变化对带宽的影响,取BW=7 GHz。但实际的时钟包含上升沿、下降沿以及非交叠时间,建立时间不会达到一个周期,所以建立时间会比一个时钟周期要短,因此在设计时取带宽BW=10 GHz。

2 前仿真验证

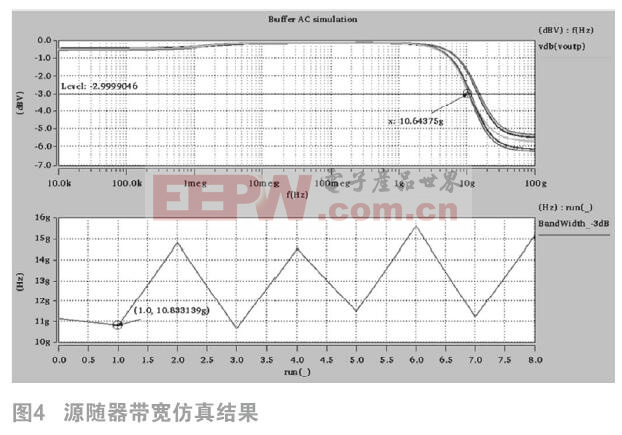

完成源随器设计后,源随器负载电容为1.5 pF,200 mV的正弦输入信号通过4.7 μF电容交流耦合进入源随器。图4为Buffer各个Corner下的带宽前仿真如图4所示(SSHT最小为10.8 GHz)。

对源随器的输出进行FFT分析,得到不同工艺角下源随器输出的线性度(SFDR),如表1所示。

前仿真可以看到,本次设计缓冲器,在低频的线性度均在85 dB以上,1.8 GHz输入信号时,线性度均在71 dB以上,满足12 bit 4 GSPS ADC的应用要求。

3 后仿真验证

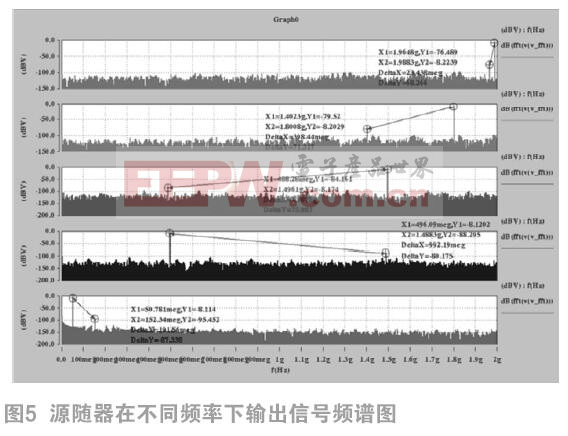

在该源随器经过前仿真验证后,充分考虑匹配和减小寄生,进行版图实现,进行寄生参数提取,完成后仿真验证。图5为TT Corner下源随器输出信号在不同输入信号频率时,输出信号的频谱,从中可以得到SFDR参数,不同Corner的统计结果如表2所示,与前仿真相比,后仿真线性度有一定的减小,最小带宽大于9.6 GHz。均满足12 bit 4 GSPS ADC的要求。

4 结论

本次设计所提出的源随器结构,适用于超高速ADC的输入信号缓冲器,解决了传统缓冲器存在的沟调效应和衬偏效应。提出了Replica的共模反馈方式,为缓冲器提供共模,解决了ADC缓冲器的输出共模在工艺角和温度变化后发生漂移的问题。仿真验证得到源随器的低频线性度均在73 dB以上,奈奎斯特频率输入的线性度均在65 dB以上,满足12 bit 4 GSPS ADC设计需要。

参考文献:

[1]M.J.Kramer,E.Janssen,K.Doris.A 14 b 35 MS/s SAR ADC Achieving 75 dB SNDR and 99 dB SFDR With Loop-Embedded Input Buffer in 40 nm CMOS[J].IEEE Journal of Solid-State Circuits.2015,12(50),:2891-2900.

[2]M.Koutani,Y.Fujimoto,M.Miyamoto.A highly linear CMOS buffer circuit with an adjustable output impedance[C].Proceedings of the IEEE 2003 Custom Integrated Circuits Conference, 2003,685-688.

[3]M.V.Campos,A.L.Fortunato,C.A.dos Reis Filho.New 12-bit source-follower track-and-hold circuit suitable for high-speed applications[C].2011 IEEE/IFIP 19th International Conference on VLSI and System-on-Chip,Hong Kong,2011, 82-85.

[4]A.M.A.Ali.A 14 Bit 1 GS/s RF Sampling Pipelined ADC With Background Calibration[J].IEEE Journal of Solid-State Circuits,2014,12(49):2857-2867.

[5]J. Matsuno, M. Hosoya, M. Furuta and T. Itakura.A 3-GS/s 5-bit Flash ADC with wideband input buffer amplifier[C].2013 International Symposium onVLSI Design, Automation, and Test (VLSI-DAT), Hsinchu, 2013,1-4.

[6]S. W. Yoon and K. W. Kwon, A source-follower with bias current regulator for enhanced linearity[C].2015 International SoC Design Conference (ISOCC), Gyungju, 2015,243-244. [7]M.Straayer.27.5 A 4GS/s time-interleaved RF ADC in 65nm CMOS with 4GHz input bandwidth[C].2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA,2016,464-465.

本文来源于《电子产品世界》2018年第6期第55页,欢迎您写论文时引用,并注明出处。

评论