晶圆级封装: 热机械失效模式和挑战及整改建议

概述

本文引用地址:http://www.eepw.com.cn/article/201708/362885.htm我们可以考虑独立封装(图6 [A])和安装在主板上的封装(图6 [B]) 两种封装工艺。本文主要讨论前者,让读者初步了解WLCSP封装的特异性。

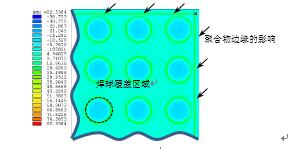

BEoL层应力如图8所示。在这样一个配置中,因为焊球和外围器件的热膨胀系数失匹,每个焊接区都会发生类似的应力问题。此外,在裸片外围可以看到聚合物层边缘的影响(见图8中的箭头)。因此,我们已开始怀疑聚合物、焊球和裸片边缘的相互作用。需要指出的是,在这个层面,应力的产生唯一原因是本地的热膨胀失匹,而与封装尺寸大小无关。

图8:BEoL区的S1 应力分量(MPa) - 独立配置(顶视图 – 重点分析封装角部)

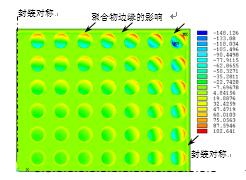

一旦组装到主板上后,应力区域特性接近在标准倒装片配置上观察到的应力区域[10]。在最外层焊球区域观察到应力最大值,因为最外层焊球到中性点(DNP)(即封装中心)的距离最远(图9)。我们还观察到,焊球下面的应力分布受焊球至封装中心的相对位置的影响。因此,压缩力和拉伸力区域方向随焊球位置不同而变化。

图9:BEoL区的SZ 应力分量(MPa) - 组装到主板上的封装 (顶视图)

与独立封装相比,已焊接的焊球使焊盘受到更大的应力。不过,无论封装尺寸多大,裸片和聚会物边缘受到的应力都会保持不变。

聚合物层

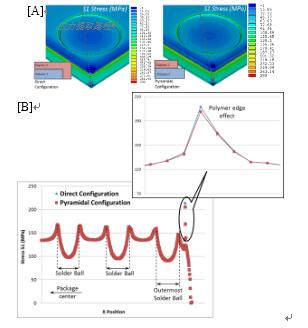

聚合物边缘可选用两种设计策略,锥体或直接沉积方法,具体选用哪一种方法,取决于第二层聚合物止于第一层薄膜之前还是之后。我们从机械学角度评测两个配置,在BEoL区域内,沿裸片对角线提取应力值(图10)。因为关注点放在了聚合物边缘,所以图中只给出了封装的角部受力情况。如前文所述,在BEoL区能够观察到焊球的影响(见图中的反复出现的图形)。此外,正如我们所预想的,在聚合物边缘发现了应力最大值,不过,应力的影响只限于这个区域。有限元分析显示,与锥体沉积法相比,直接沉积法的应力更高,这是因为前者边缘处聚合物厚度较大。两种沉积方法导致厚度相差大约5% (图10 (B))。

图10:[A] 直接配置和锥体配置的BEoL层和聚合物层应力分布图[B] BEoL栈周围应力变化(见应力提取通道图[A]上的灰箭头) (独立封装配置)

在决定了边缘设计方法后,我们需要确定在BEoL栈上发生较低应力的准确位置。为此,我们测试了各种位置:平坦区(图11 #1, #4)、密封环(图11 #6)上方、钝化拓扑底部不同位置(图11 #2 #3 #5)。

图11:有聚合物的配置与无聚合物的配置之间的应力变化。在SiN钝化层内提取拉伸应力Sy。不同配置间的应力差异主要出现在聚合物边缘。

鉴于聚合物末端在BEoL栈上产生拉伸性负载,确定选项#6为首选。因此,密封环的‘锚定’特性可限制其潜在的不利影响。为辨别结构差异,关注点放在钝化层应力上。

不出所料,发现两个大类:第一类(#2, #3 & #5)是聚合物层末端靠近一个几何奇点,引发最大应力;第二类(#1, #4 & #6)是聚合物层末端在一个平坦面上,这里观察到最小应力。提案#6(即密封圈上方)的改进作用并不明显,需要说明地是,这可能是所用分析标准造成的,本文只分析了SiN层的完整性,BEoL中间层的离层风险并未视为一种失效模式。基于这些结果和过程可变因素,将边缘置于较大的平坦区域是比较安全的,这对应配置#4。

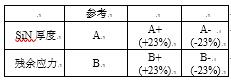

钝化性质

聚合物层边缘、暴露于空气中的结构和焊盘的存在,让WLCSP封装的钝化层成为一个重要区域。开发人员可以从厚度和残余应力角度探讨最佳设计。因为我们跟踪的失效类型是机械失效,所以讨论重点放在氮化物层的特性方面。为此,我们测试了不同厚度与残余应力的相对变化,见表1.

表1.探讨过的参数表

图12:[A]SiN厚度的影响[B]SiN残余应力的影响

应力是从聚合物层下面的SiN层提取的(图12)。测试结果显示,SiN越厚,应力越小。还应记住,如果厚度较大,真层拓扑可能会更平滑,奇点更少,因此,可降低失效风险。关于残余应力影响,根据最初假定值,最终应力被迁移。因此,通过降低残余应力,降低了最终应力状态的数学值。不过,增加厚度方法不能随意修改,还要记住对其它特性(例如,电气、可靠性和热变形)的影响。因此,必须找到一个折衷的办法,考虑到所有的副作用。

4. 结论

本文概述了WLCSP晶圆级封装的特异性,先简要介绍了扇入和扇出型封装特异性以及封装流程;然后,描述了在制程工序和/或可靠性测试期间发生的不同的热机械失效。裸片边缘带和焊球四周是高度敏感区域,发生过很多失效问题。为更深入地了解所涉及的结构,本文采用有限元法分析了WLCSP封装失效问题。首先,建立一个3D封装模型,初步了解扇入型封装的热机械特性。研究发现,焊球和聚合物边缘是影响可靠性的重要位置。然后,用一个2D模型深入分析聚合物边缘的影响,优化BEoL层。实验发现,终止在平坦区域的锥体沉积法可降低在BEoL钝化层发生的应力。最后,我们研究了SiN厚度及残余应力的影响,并建议提高SiN层厚度,以降低残余应力。

本文能够让读者朋友更好地了解WLCSP封装在机械性能方面的特异性。通过介绍一组与有限元法结果相关的典型失效,我们概括了主要有效参数和可靠性改进建议。

参考文献

1.Xuejen Fan, Qiang-Han, Reliability challenges and design considerations for Wafer-Level packages, Electronic Packaging Technology & High Density Packaging conference (ICEPT-HDP), 2008

2.Xuejun Fan, Wafer Level Packaging (WLP):Fan-in, Fan-out and Three-Dimensional Integration, Eurosime Conference, 2010

3.Cadmus Yuan et al., Design and Analysis of a novel fan-out WLCSP structure, Eurosime Conference, 2006

4.Hikaru Nomura et al., WLCSP CTE Failure Mitigation via Solder Sphere Alloy, ECTC, 2015

5.K. M. Chen, Lead-Free Solder Material and Chip Thickness Impact on Board-Level Reliability for Low-K WLCSP, IEEE Transactions on advanced packaging, vol. 33, no. 2, 2010

6. Reche, J.H.J. and Kim, D.H., Wafer level packaging having bump-on-polymer structure, Microelectronics Reliability, 43, 879-894, 2003

7.Kim D-H, Elenius P, Johnson M, Barrett S. Solder joint reliability of a polymer reinforced wafer level,package, Microelectronics Reliability, 42,1837, 2002

8.Bumping Design Guide, [online], Available: http ://www.flipchip.com/

9.Ming-Che Hsieh, Modeling Correlation for Solder Joint Fatigue Life Estimation in Wafer-Level Chip Scale Packages, IMPACT conference, 2015

10.Gallois-Garreignot et al., Chip Package Interactions:Package Effects on Copper Pillar bump induced BEoL Delaminations &Associated Numerical Developments, ECTC, 2015

评论