一篇文章说清半导体制程发展史

有朋友补充说,这种金属是钨,我查阅到资料也提到是钨;钨本身也用在后端的via中; 但是在这个问题上我有些保留,主要原因是4点:

本文引用地址:http://www.eepw.com.cn/article/201707/361285.htm第一, 我自己上课的时候,有多位教授都明确提到过,关于这个metal gate的资料外界知之甚少,至少他们自己不知道,或因为某种原因而不愿意说;

第二,从原理上说,对于NMOS和PMOS,因为所需的功函数是不一样的,所以单一的一种金属无论如何是不可能满足整个high-k工艺的需求,即使确实是钨,也需要进行work function engineering;

第三, 也有很多资料提到了别的材料,譬如说TiN 系列作为metal gate;

第四, 或许也是最令人疑惑的,就是在我查阅过的资料中,虽然Intel很早就说使用了HfO2作为high-k材料,但是Intel自己却没有透露这种或这几种金属是什么,它在2008年发表的iedm的文章,并没有提及具体的材料,而是以“metal gate”作为代称。Mark Bohl在2007年发表的文章中,也明确说到如下的信息:

“Because the electrical characteristics of the gates of NMOS and PMOS transistors are different, they actually needed not one metal but two—one for NMOS and one for PMOS.”

“But by themselves, none had exactly the work function of the doped silicon, so we had to learn to change the work function of metals to suit our needs.”

“We cannot disclose the exact makeup of our metal layers, because after all, the IC industry is very competitive!”

更新的资料中,似乎也没有找到相关的信息,而是多以WFM (work function metal)作为指代。虽然在研究界有过关于W、TiN等多种材料的不少研究论文发表,但是我自己是无力确认关于这个metal gate材料的信息来源是什么。因为本人并不从事晶体管制造或设计的研究工作,无力回答这个问题。因此希望能有知情的朋友进行补充,并且提供来源。

于是摩尔定律再次胜利。

32nm第二代high-k绝缘层/金属栅工艺。

在45nm时代,英特尔取得了巨大的成功(在很多晶体管、微处理器的发展图上,45nm这一代的晶体管,会在功耗、性能等方面突然出现一个较大的进步折线),32nm时候继续在基础上改换更好的材料,继续了缩小尺寸的老路。当然,前代的Ge strain工艺也是继续使用的。

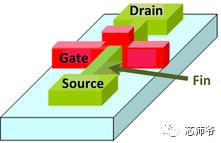

22nm FinFET(英特尔称为Tri-gate),三栅极晶体管。

这一代的晶体管,在架构上进行了一次变革。变革的最早设计可以追溯到伯克利的胡正明教授2000左右提出的三栅极和环栅晶体管物理模型,后来被英特尔变为了现实。

FinFET 一般模型长这样。它的实质上是增加了一个栅极。

为什么要这么做呢?直观地说,如果看前面的那张“标配版”的晶体管结构图,在尺寸很短的晶体管里面,因为短沟道效应,漏电流是比较严重的。而大部分的漏电流,是通过沟道下方的那片区域流通的。

沟道在图上并没有标出来,是位于氧化绝缘层以下、硅晶圆表面的非常非常薄(一两个纳米)的一个窄窄的薄层。沟道下方的区域被称为耗尽层,就是大部分的蓝色区域。

于是有人就开始想啊,既然电子是在沟道中运动,那么我为何非要在沟道下面留有这么一大片耗尽层呢?当然这是有原因的,因为物理模型需要这片区域来平衡电荷。但是在短沟道器件里面,没有必要把耗尽层和沟道放在一起,等着漏电流白白地流过去。

于是有人(IBM)开了一个脑洞:把这部分硅直接拿掉,换成绝缘层,绝缘层下面才是剩下的硅,这样沟道就和耗尽层分开了,因为电子来源于两极,但是两极和耗尽层之间,被绝缘层隔开了,这样除了沟道之外,就不会漏电啦。比如这样:

这个叫做SOI(绝缘层上硅),虽然没有成为主流,但是因为有其优势,所以现在还有制造厂在搞。

于是有人(英特尔)又想了,既然都是拿掉耗尽层的硅,插入一层氧化层,那么为什么非要放上一堆没用的硅在下面,直接在氧化层底下,再弄一个栅极,两边夹着沟道,岂不是更爽?你看你IBM,就是没雄心。

但是英特尔还觉得不够,又想,既然如此,有什么必要非得把氧化层埋在硅里面?我把硅弄出来,周围三明治一样地包裹上绝缘层,外面再放上栅极,岂不是爽爆?

于是就有了FinFET,上面这种。FinFET牛逼的地方在于,不仅大大降低了漏电流,而且因为多一个栅极,这两个栅极一般都是连在一起的,大大增加了前面说过的那个绝缘层电容,也就大大提升了晶体管的开关性能。所以又是一次革命式的进步。

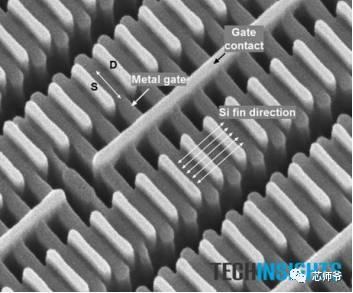

这个设计其实不难想到,难的是,能够做到。为什么呢?因为竖起来的那一部分硅,也就是用作沟道的硅,太薄了,只有不到10个纳米,不仅远小于晶体管的最小尺寸,也远小于最精密的光刻机所能刻制的最小尺寸。于是如何把这个Fin给弄出来,还得弄好,成了真正的难题。

英特尔的做法是很聪明的,解释起来需要很多张工艺流程图,不多说,但是基本原理是,这部分硅不是光刻出来的,而是长出来的。它先用普通精度的光刻刻出一堆“架子,然后在沉淀一层硅,在架子的边缘就会长出一层很薄的硅,然后再用选择性的刻蚀把多余的材料弄走,剩下的就是这些立着的、超薄的硅Fin了。当时我听说这套方法的时候,彻底跪了,这智商太碾压人了。

FinFET的工艺流程

制作FinFET的工艺流程具体是怎样的呢?笔者并非这方面的专家,所知有限。尽所能查阅了一些资料之后,把相关的一些信息整理在下面,供大家参考。

在2016年8月的这篇访谈中,Intel的Mark Bohl (Senior fellow and director of process architecture and integration)谈到了Intel的FinFET技术,以及对于10nm制程的技术展望。在其中,他提到Intel将会继续使用SADP (Self-Aligned Double Patterning)工艺。

Double Patterning是可以提高光刻最小精度的,是目前主流采用的一种技术,有很多个版本。它的原理是这样的,譬如说,Intel是采用193nm的浸入式光刻来处理最高精度需求的步骤,这个技术的最小尺寸大约是80~90nm之间。如果使用Double Patterning的话呢,则可以将这个精度提高到约40nm左右。

这个在原理上是很容易理解,如果先pattern一批80nm精度的图样,然后再交错着pattern一批80nm精度的图样,在两次光刻之后,图样的精度,以pitch来衡量的话,就会是原来的精度的一半。这个过程在维基百科中就有说明,大家可以直接查阅

Multiple patterning。

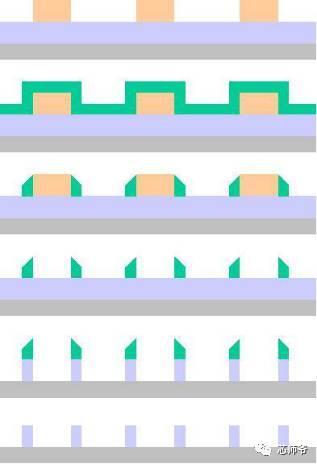

Self-Aligned Double Patterning是其中的一种技术,它只需要一次光刻步骤就能完成,而且从原理上说,是可以用来制作fin的(制作fin的这个步骤叫做active fin formation)。我在上一些相关的器件和工艺课程的时候,自己的教授也有提到这个工艺是被用来制作fin的。但是在这方面,我并没有找到直接的资料,来自Intel 或别的几个大厂,来说明自己的active fin formation具体是怎么做的,因此这只能算是一个合理的猜测。

在这个过程中,首先会沉积一层hard mask,又被称作mandral的材料,比如Si3N4之类的。这层材料以普通精度的光刻进行pattern。mandral在被pattern之后,就被称作spacer。然后再生长一层绝缘层材料,譬如二氧化硅,被称作film。

可以通过控制这个生长过程的时间,来控制最终的fin的厚度W。然后对film进行刻蚀,将所有水平方向的材料刻蚀掉,只剩下沿着spacer的边缘所生长出来的那部分,之后再以选择性的刻蚀将spacer材料移除,只剩下这层sidewall film。最后就是对底下的硅材料进行刻蚀,这样相当于用这层film做了mask。

接下来,为了保证isolation,还需要再生长一层绝缘材料二氧化硅,这个步骤要求很高,因为fin和fin之间的那段空间,高宽比是很大的,需要让二氧化硅完全填充这个空隙,所以这个步骤被称作conformal coating。

显然这个步骤之后,硅片的表面是不平整的,因此需要进行一次CMP (Chemical Mechanical Polishing),就是通过添加一定的研磨剂,用机械研磨的方式将整个晶圆的表面给弄平整。

最后就是再对二氧化硅材料进行一次刻蚀,通过控制这次刻蚀的时间,可以控制露出来的fin的高度H。在这个fin上面,再用ALD (Atomic Layer Deposition)等步骤沉积high-k材料等栅极的stack,就基本完成了这部分的制作。

上面这个工艺确实是存在的,也是被采用的,然而关于它有一个问题,就是我所能找到的资料,似乎显示这个工艺是被IBM、三星这系列的厂,用在SOI的finfet上面。

前面提到过SOI的概念,这里应该补充一下,其实SOI和finfet并不是两种对立的技术,之前的比较,只是为了方便从晶体管物理的角度解释两种技术的思路是什么。finfet也是可以制作在SOI晶圆上面的,这是三星它们的做法。

但是Intel似乎并没有采用这种做法,出于成本的考虑(SOI晶圆比较贵),Intel使用的是bulk finfet,沟道底下是没有埋绝缘层的。那么在这个制程下面,active fin formation是否也是用SADP这样的工艺制备的?我没有找到直接的资料证据。

虽然在一些采访和报道中,Intel提到自己是用了SADP工艺,但是这个工艺并不限于制作fin,也可以用在制作栅极的pattern以及后端的via, interconnect上面,因此我不能确定Intel 是怎么做的。

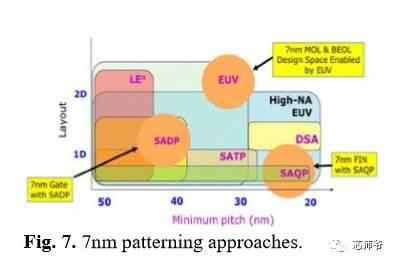

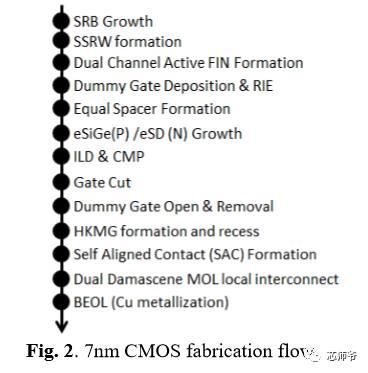

三星在IEDM上发表过他们最新的7nm工艺晶体管的报告中的几张图,概述了三星IBM(这俩是一家人...)这个系列的工艺制程的思路,它们是这样考虑的:

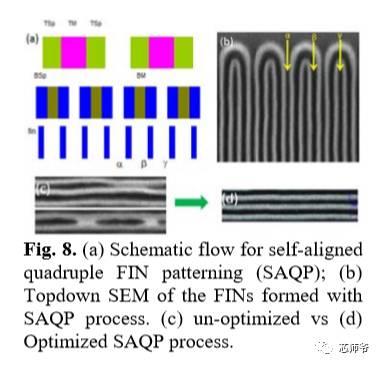

可以看到三星是用SAQP(self-aligned quadruple patterning, 和SADP流程基本一样,而又增加了一次光刻,因此最小尺寸进一步缩小 )来进行7nm fin制备,如下图所示:

它也提到了整个流程,可是我自己完全看不懂

台积电在同一个会议中也发表了7nm,但是语焉不详。Intel则没有发表。在Intel发表的14nm晶体管的文章中,同样只有一句话提到使用了SADP工艺,但是并没有像三星这样细致地说明工艺步骤,而是直接开始讲晶体管的性能,所以在这方面的信息很少。

需要说明一下,无论是哪个工艺,其实一开始都不是这些公司自己发明的,譬如说,胡正明教授就曾经发表过SADP相关的文章,那是早在2006年finfet出来之前多年。

这些公司看重了某个工艺的前景(能不能scale,成本问题,等等),然后将它整合到自己积累多年的制作流程中去,推出新一个节点的制程。因为完成一个工艺的设备成本是极其高昂的,所以往往需要提前多年就做好规划。

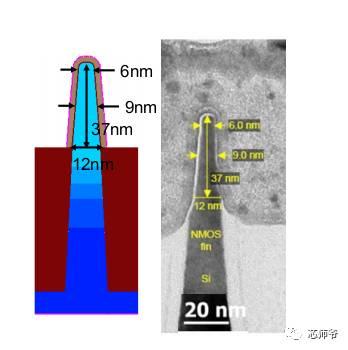

14nm 继续FinFET。下面是英特尔的14nm晶体管的SEM横截面图,大家感受一下,fin的宽度平均只有9nm。

当然,在所有后代的技术节点中,前代的技术也是继续整合采用的。所以现在,在业界和研究界,一般听到的晶体管,都被称作high-k/metal gate Ge-strained 14 nm FinFET,整合了多年的技术精华。

而在学术界,近些年陆续搞出了各种异想天开的新设计,比如隧穿晶体管,负电容效应晶体管,碳纳米管,等等。

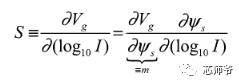

所有这些设计,基本是4个方向:材料、机理、工艺、结构。而所有的设计方案,其实可以用一条简单的思路概括,就是前面提到的那个SS值的决定公式,里面有两项相乘组成:

因此,要么改善晶体管的静电物理(electrostatics),这是其中一项,要么改善沟道的输运性质(transport),这是另一项。

而晶体管设计里面,除了考虑开关性能之外,还需要考虑另一个性能,就是饱和电流问题。很多人对这个问题有误解,以为饱不饱和不重要,其实电流能饱和才是晶体管能够有效工作的根本原因,因为不饱和的话,晶体管就不能保持信号的传递,因此无法携带负载,换言之只中看,不中用,放到电路里面去,根本不能正常工作的。

举个例子,有段时间石墨烯晶体管很火,石墨烯作沟道的思路是第二项,就是输运,因为石墨烯的电子迁移率远远地完爆硅。但直到目前,石墨烯晶体管还没有太多的进展,因为石墨烯有个硬伤,就是不能饱和电流。但是,去年貌似听说有人能做到调控石墨烯的能带间隙打开到关闭,石墨烯不再仅仅是零带隙,想来这或许会在晶体管材料方面产生积极的影响。

在去年的IEDM会议上,台积电已经领先英特尔,发布了7nm技术节点的晶体管样品,而英特尔已经推迟了10nm的发布。当然,两者的技术节点的标准不一样,台积电的7nm其实相当于英特尔的10nm,但是台积电率先拿出了成品。三星貌似也在会上发表了自己的7nm产品。

可以看出,摩尔定律确实放缓了,22nm是在2010左右出来的,到了现在,技术节点并没有进步到10nm以下。去年,ITRS已经宣布不再制定新的技术路线图,换言之,权威的国际半导体机构已经不认为,摩尔定律的缩小可以继续下去了。

这就是技术节点的主要现状。

技术节点不能进步,是不是一定就是坏事?其实不一定。28nm这个节点,其实不属于前面提到的标准的dennard scaling的一部分,但是这个技术节点,直到现在,仍然在半导体制造业界占据了很大的一块市场份额。

台积电、中芯国际等这样的大代工厂,都是在28nm上玩得很转的。为何呢?因为这个节点被证明是一个在成本、性能、需求等多方面达到了比较优化的组合的一个节点,很多芯片产品,并不需要使用过于昂贵的FinFET技术,28nm能够满足自己的需求。

但是有一些产品,比如主流的CPU、GPU、FPGA、memory,其性能的提升有相当一部分来自于工艺的进步。所以再往后如何继续提升这些产品的性能,是很多人心中的问号,也是新的机会。

评论