选择正确的FPGA设计工具

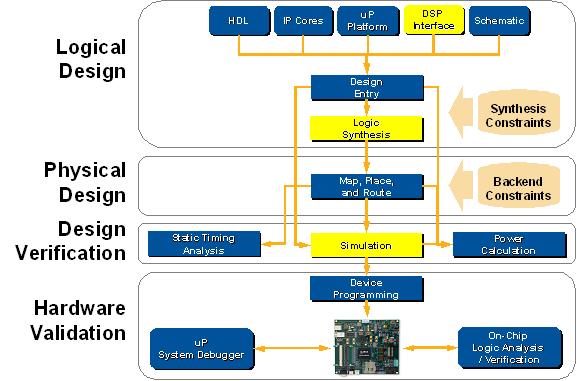

FPGA设计流程(图1 )包括逻辑设计和物理设计,设计验证和硬件验证。一些FPGA厂商只提供厂商专有的设计工具,而另一些FPGA厂商则提供第三方工具和厂商专有工具的组合。第三方工具主要用于“前端”的综合和仿真,而厂商的专有工具专注于 “后端”的物理设计和硬件验证。

逻辑设计

逻辑设计包括几乎能用于所有应用的各种输入方式,如VHDL、Verilog、知识产权核、嵌入式处理器,顶层电路图和DSP模块。

图1中的设计输入是简化的示意图,这个阶段也可能需要HDL Linting (检查是否违反语法规则,优选的代码风格,以及设计规划)。在设计的早期阶段还可以进行I / O规划,针对团队协作的设计划分,早期静态时序分析和功率计算等。

物理设计

随着设计规划过程的进行,添加的物理约束会影响映射,布局和布线。物理设计看起来比较直观,然而,这个阶段中要满足时序要求,以及添加关键功能以产生所需的系统解决方案,因此验证是至关重要的。

设计验证和硬件验证

一旦设计完成,问题就转换成,这个设计是否能正常工作?设计验证工具包括静态时序分析,时序仿真和功耗计算,这些工具用来确保建立和保持时间满足时序要求,关键路径满足性能要求,以及电源供应足以满足系统功耗等等。如果设计不能正常工作,还有更多的工具可用来进行逻辑分析,甚至软件代码调试。

选择正确的FPGA设计工具

选择设计工具时,决定的部分因素是所选的芯片,因为设计流程的物理( “后端” )部分总是芯片供应商专有的。然而,做选择设计工具的决定时,还应该认真评估综合和仿真工具(“前端”)的性能和功能。

拥有第三方综合和仿真工具的FPGA设计工具套件可以为用户提供更高的价值。针对前端设计任务的第三方工具通常是优异的,因为EDA供应商致力于以下几个方面的努力:

专注于设计工具

为了保持竞争力,必须不断完善他们的工具

根据对EDA市场的广泛和全面的了解,以及客户的需求来设计工具

必须提供适应不同设计流程要求的工具

例如,在莱迪思的ispLEVER设计工具套件中,我们选择了第三方工具实现综合,以及功能和时序仿真。目前,该莱迪思工具套件包括Synplify ®的专业版本和Aldec Active-HDL的莱迪思版本。

第三方工具的优点

Synplify Pro

莱迪思软件中集成的Synplify Pro是一种先进的FPGA综合的解决方案,提供优异的性能和高效率的设计。该工具还包括Synplicity的HDL分析工具,使用户能够快速的进行调试和改进Verilog或VHDL代码。该工具为用户提供RTL 或门级的图形表示,并可以在RTL和图形表示之间进行交叉定位。

Active-HDL

在Aldec Active-HDL的莱迪思版本中,可以在单个设计中进行VHDL和Verilog的混合仿真。此外,项目管理,设计输入(包括语言助手、层次化显示,脚本生成和测试平台生成)以及调试和分析工具(如代码跟踪,断点管理,波形编辑和浏览)都集成在这个验证平台。

结论

在综合和仿真方面,EDA供应商是公认的专家;而在物理设计和硬件验证方面,只有FPGA厂商能设计和提供为芯片专门优化的后端工具。我们的经验是借助于领先EDA供应商的专业技术使FPGA设计工具套件为用户提供更高的价值。

评论