胡正明续写摩尔传奇 FinFET/FD-SOI厂商如何押宝?

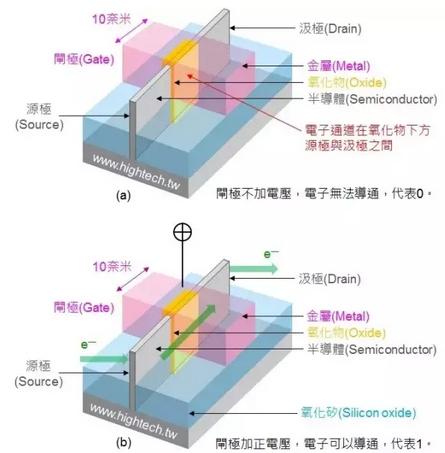

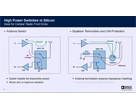

FinFET呈立体板状结构,闸极与通道之间的接触面积变大了,即使擅长缩小到 20nm以下,仍然可保留很大的接触面积,可以控制电子是否能由源极流到漏极,因此可以更妥善的控制电流,同时降低漏电和动态功率耗损。这就是为摩尔定律“续命”的原因了。

本文引用地址:http://www.eepw.com.cn/article/201702/343986.htm

此处,我们不得不提到一个人,梁孟松。胡正明教授是梁孟松的博士论文指导教授,也就是说,梁孟松是FinFET技术的核心人物之一。

曾经,台积电没有重用梁孟松继续研发此技术,而他跳糟到三星, 于是三星的 FinFET 制程技术突飞猛进甚至超越台积电。

虽然台积电控告梁孟松侵权与违反竞业禁止条款获得胜诉,但是这却带来一场台湾半导体晶圆代工产业的重大危机。

相比FinFET,FD-SOI阵营要冷清很多,英特尔与台积电似乎已经将FinFET当成标准技术。

FD-SOI要比FinFET落后?答案是否定的。

与FinFET技术相比,FD-SOI的优势更为明显。

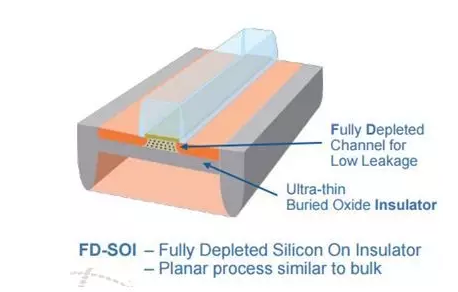

FD- SOI(全耗尽绝缘层上硅)技术仍然采用平面型晶体管,其硅薄膜可自然地限定源漏结深,同时限定了源漏结的耗尽区,从而可改善DIBL(漏致势垒降低)等短沟道效应,改善器件的亚阈特性,降低电路的静态功耗。此外,FD-SOI晶体管无需沟道掺杂,可以避免RDF(随机掺杂涨落)等效应,从而保持稳定的阈值电压,同时还可以避免因掺杂而引起的迁移率退化。

体偏压技术(body-bias)是FD-SOI技术所独有的特点,也是让该技术最受关注的特点。通过把硅做得极薄,让它可以全部耗尽,所以不会再漏电流。如果再将氧化硅层做的非常薄,同时放入偏置装置(bias),就可以调节控制这个晶体管。如果放入的是正偏压,可以实现性能快速增强;如果放入的是负偏压,我们实际上可以关掉该装置。让它实现很低的漏电流,大概是1pA/micron的水平。

FD-SOI向后兼容传统的成熟的基板CMOS工艺。

在莫大康《SOI与FinFET技术谁更优》一文中可看到FD-SOI有以下几大优势:

SOI工艺的优势:

1. 减少寄生电容,提高器件频率,与体硅相比SOI器件的工作频率提高20-35%。

2. 由于减少寄生电容和降低漏电流,SOI器件的功耗相比体硅下降35-70%。

3. 消除了闩锁效应(闩锁效应,即Latch up, 是指CMOS芯片中,由于寄生的PNP和NPN双极性BJT相互影响而产生 在电源和地线之间的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流。)。随着IC制造工艺的发展,封装密度和集成度越来越高,产生闩锁效应的可能性会越来越大。

4. 抑制衬底的脉冲电流干涉,减少软错误的发生。

5. 与硅工艺相容,可减少13-20%工序。

胡教授曾说:“我当时觉得我们恐怕没有办法搞到可以满足这种条件的SOI基体,没有公司能够对外供应硅膜厚度仅有5nm的SOI晶圆。我当时觉得这不太可能实现,或者说等人们具备这种技术能力时,FinFET技术可能已经得到了充分的发展。不过两年前法国Soitec公司改变了这种情况,他们开始推出300mm UTB-SOI的晶圆样品,这些晶圆的顶层硅膜原始厚度只有12nm,然后再经处理去掉顶部的7nm厚度硅膜,最后便可得到5nm厚度的硅膜。这便为UTB-SOI技术的实用化铺平了道路。”

如何押宝?

半导体厂商应该押宝FinFET还是FD-SOI工艺技术?这个问题在业内讨论已久,偏向FinFET的似乎要多一些。因为大部分半导体厂商的开发工作方向转向了FinFET技术。

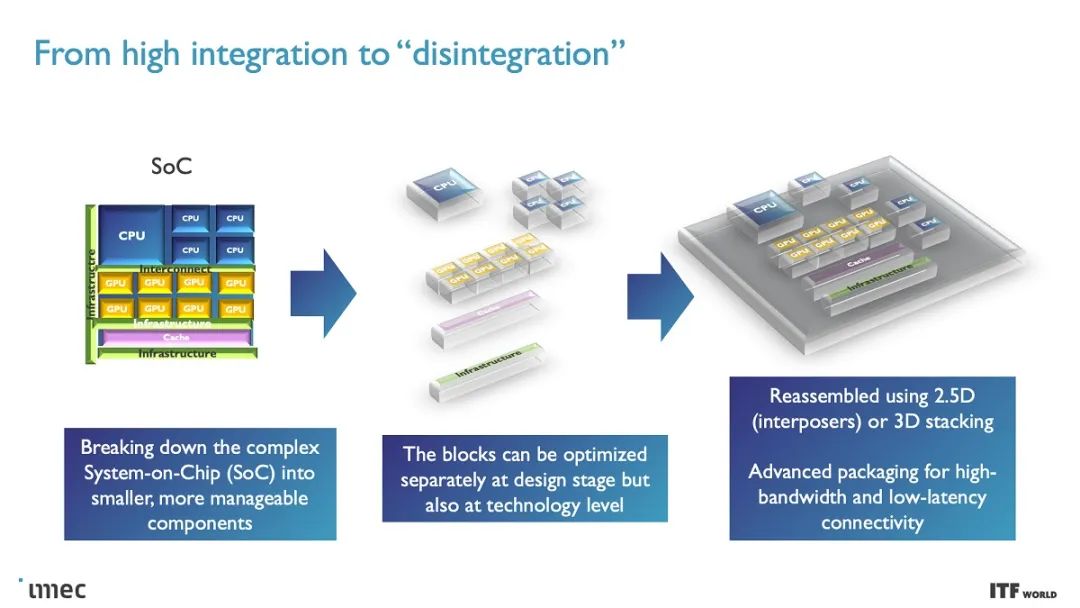

胡正明教授认为,FinFET和UTB-SOI技术是可以并存的,不过在未来几年内,两者都会想尽办法彼此超越对方成为主流技术。现在Intel采用了FinFET技术,原因是这种技术可以让微处理器的性能相对更强;而台积电、格罗方德或三星等晶圆代工厂,必须要同时提供以上两种工艺产能服务客户。

胡正明教授曾推测:台积电公司会在14nm节点开始采用FinFET技术,然后则会为低功耗产品的用户推出应用了UTB-SOI技术的产品。而联电公司则会减轻对FinFET技术的投资力度,并直接转向UTB-SOI技术。而事实的确如此。

除了FinFET与FD-SOI,胡正明教授还有诸多的科学贡献,比如领导研究出BSIM,从实际MOSFET晶体管的复杂物理推演出数学模型,该数学模型于1997年被国际上38家大公司参与的晶体管模型理事会选为设计芯片的第一个且唯一的国际标准;首先提出热电子失效的物理机制,开发出用碰撞电离电流快速预测器件寿命的方法,并且提出薄氧化层失效的物理机制和用高电压快速预测薄氧化层寿命的方法;首创了在器件可靠性物理的基础上的IC可靠性的计算机数值模拟工具。

在这个微缩时代,胡正明教授鼓励半导体从业人员保持信心,曾讲到:“产业的进步需要我们通过不断的改进,过去五十年是这样走过来的,相信未来五十年也会这样走下去。”

评论