一种读写深度可配置的异步FIFO设计

引言

随着设计复杂度的不断提高,现代电子信息设计中,单一时钟驱动已无法满足设计与应用的需求。基于多时钟驱动的设计已经越来越普遍,在异步时钟域的设计中,跨时钟域数据信号传输是必须考虑的一个问题。控制信号一般使用握手协议来实现异步传输,对于异步时钟域大数据量的传输则经常使用异步FIFO来实现。

基于FIFO进行跨时钟域数据传输的具体设计,主要借助于FIFO的空/满状态信号来控制对FIFO的读写操作。在部分使用处理器检测空/满状态标志的设计中,当FIFO已经空或满时,处理器会出现来不及响应的情况,从而造成数据的溢出或者数据流的断流现象。这无法满足一些设计的严格要求,所以就有了半空/半满标志的使用。但针对一些大容量的FIFO,简单使用半空/半满标志进行FIFO的读写控制时,因为具体应用的不同,会有部分FIFO的存储资源没有使用,造成硬件资源的浪费。

针对这一现状,本文提出一种读写深度可配置的FIFO设计。通过对寄存器的配置,来设定产生有效FIFO读写控制信号时FIFO的深度。在提高硬件资源利用率的同时,还可以通过寄存器的配置,使设计满足于不同的具体应用。

1 异步FIFO的工作原理简述

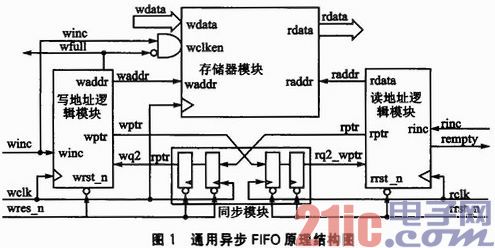

通用异步FIFO的原理结构图如图1所示。由图中可以看出,异步FIFO由4部分组成:存储器模块、写地址逻辑模块、读地址逻辑模块、同步模块。其中,写地址逻辑模块和读地址逻辑模块是两个相互独立的时钟域模块。

FIFO的空/满状态的判断是FIFO设计中的一个关键部分,主要通过对读/写地址的比较来实现。鉴于读/写地址的控制逻辑分别工作在各自的时钟域下,进行比较时,通常将二进制码的地址转换为格雷码的编码方式,传输到异步时钟域再进行比较,以使亚稳态的产生处于可以接受的范围之内。对于FIFO的读写,当FIFO的满状态信号有效时,禁止写操作;当FIFO的空状态有效时,禁止读操作。

2 深度可配置的异步FIFO设计

本文所提出的深度可配置异步FIFO的设计,在通用异步FIFO的基础上,增加半空/半满状态标志的产生,同时通过寄存器的配置,可动态调整所增加状态标志的产生条件,从而实现应用中的深度可配置。其接口框图如图2所示。

各接口的说明为:wdata为写入数据,rdata为读出数据;wrst_n为写时钟复位信号,rrst_n为读时钟复位信号;wr_en为写使能信号,rd_en为读使能信号;welk为写时钟,rclk为读时钟;full为输出满状态信号,empty为输出空状态信号;hempty为半空信号,hfull为半满信号;具体半空半满信号的产生可由rd_depth_reg与wr_depth_reg控制。

在采用此FIFO的设计中,full与empty信号分别用于控制写操作与读操作。当full有效时,禁止写操作。同样,当empty有效时,禁止读操作,从而避免写覆盖与读空的发生。但是在数据路径中,为了防止读数据流的间断,在半空状态时就会开始写操作;在半满状态时就开始读操作,防止写满后禁止写操作再进行读取造成数据的丢失。

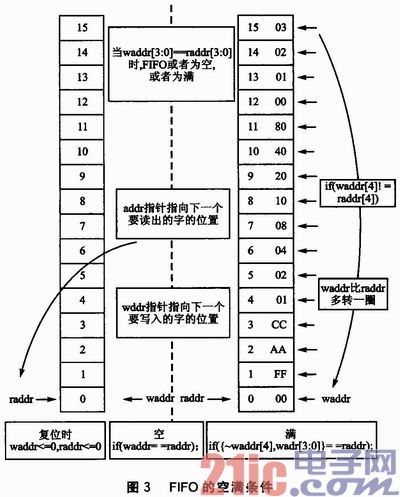

在FIFO的逻辑设计中,空/满及半空/半满状态标志的产生都是由读/写地址的指针来判断的。对于空状态主要有两种情况:复位时读/写指针相等或者读指针赶上写指针状态。但是,若写指针循环一次赶上读指针时,此时读/写指针相等应该为满状态。所以,单独的从读/写指针是否相等不能判断是空状态还是满状态。

一种区分空和满状态的设计方法是,对两个指针各增加一个冗余位。当写指针增加到最后的FIFO地址时,写指针将增加没有用到的最高位,同时复位其他位,FIFO的空满条件如图3所示(FIFO转过一圈,并置位最高位)。读指针也是同样的情况。如果两个指针的最高位是不同的,则意味着写指针比读指针多转了一圈。如果两个指针的最高位是相同的,则意味着两个指针转过了同样的圈数。n位的指针中,用n-1位来指向整个FIFO的内存缓冲区。当两个指针包括最高位在内的所有位都相等时,FIFO为空。当两个指针除了最高位外,其他位都相等时,FIFO为满。

半空/半满状态信号的产生与空/满状态类似,根据对读写指针除去冗余位差值的比较,来判断半空半满状态。当冗余位相同时,半满信号为写指针减去读指针大于FIFO物理深度的一半,半空信号则为差值小于FIFO物理深度的一半。当冗余位不同时,半满信号为读指针减去写指针小于FIFO物理深度一半,半空信号为差值大于FIFO物理深度的一半。

在部分实际应用中,若严格按照半空/半满条件,虽然保证了数据的不丢失,但数据突发传输的深度仅为FIFO物理深度的一半,从而造成了对硬件逻辑资源的浪费。因此,对于半空/半满状态标志的判断,临界值采用寄存器配置的方式保证数据的不丢失,同时又尽可能地利用现有FIFO的存储资源,提高数据吞吐率。

结语

本文对异步FIFO的工作原理进行了简单介绍,同时提出了一种深度可配置的异步FIFO的设计方法。这种深度可配置的异步FIFO的设计方法,对于含有DMA外设的电路及在高速数据传输系统中,可进行高效可靠的数据读取操作,同时可提高硬件资源的利用率。

评论