基于DSP+CPLD的高性能金属磁记忆检测仪的设计与实现

0引言

本文引用地址:https://www.eepw.com.cn/article/201610/308514.htm金属磁记忆检测技术自提出后一直具有良好的应用前景,但其理论研究的不足是制约该技术应用和发展的一大瓶颈,现有的理论研究认为,铁磁材料结构表层的隐性缺陷会产生法向磁场分量过零值点,使得切向磁场分量取最大值。据此市场上一些检测仪就是以法向磁场分量过零值点来判断铁磁材料应力集中区域。现今,国内外一些学者在此基础上做更多的研究,有一部分学者,通过测量磁场信号,得到了磁场梯度,根据磁场梯度来判断磁记忆损伤程度;另有一些学者,通过小波变换对采集的磁场信号进行抑制细节系数、小波指数下降消噪等多种方法的分析处理,利用多种特征量对应力集中进行定性和定量的综合判断,来提高对铁磁性金属构件疲劳损伤的识别率。

总之,这些方法都是在测量到铁磁材料漏磁信号的基础上建立的,本文设计的金属磁记忆检测仪是以DSP和CPLD为核心的嵌入式设备检测系统,由于DSP艺芯片处理速度快,能对实时采集数据进行高速处理,但DSP芯片资源、接口都有限,与外设的配合常常面临接口复用、时序配合等要求。为减少DSP因对片外模块进行控制、通信等所带来的时间开销,高效发挥DSP的数据处理能力,本文实现了一种基于 CPLD的外围控制枢纽,协助DSP芯片完成外设的逻辑控制和时序协调,保证了DSP芯片的数据处理速度。

1硬件接口设计

系统中DSP采用的是TI公司的TMS320F28335处理器,CPLD采用的是ALTERA公司的 EPM570,传感器选用的是HONEYWELL公司的HMC1052磁阻传感器,液晶显示屏选用的是深圳旭升达电子厂生产的HW480272F-0L- 0A型号TFT液晶显示屏。

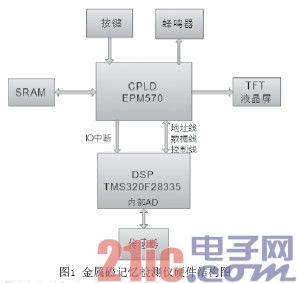

系统整体实现流程为:传感器采集铁磁性零件表面的磁记忆信号,DSP通过内部自带AD转换器,对传感器的信号进行快速采集、高速处理、提取特征信号后,DSP通过总线方式将信号传给CPLD,CPLD将波形显示信号存入显存SRAM中,然后再将SRAM中存储的 TFT显示屏的一帧波形数据在TFT屏上用波形显示,因此一旦屏上波形出现过零点,即可判断此处存在应力集中。为了方便系统的人机交流,系统中增加了按键和蜂鸣器,按键负责系统相关参数的设定,当检测到应力集中区域时,蜂鸣器负责报警。图1为检测仪的硬件结构图。

1.1HMC1052磁阻传感器

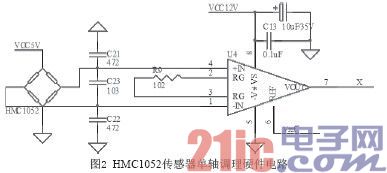

磁阻传感器HMC1052是一个双轴线性磁传感器,每个传感器有一个由磁阻薄膜合金组成的惠斯通桥。当加上供电电压,传感器将磁场强度转换为电压输出,通过一个仪用放大器即可将信号电压放大到AD采样电压量程范围。HMC1052的磁场测量范围是±6gauss,灵敏度是1.0mV/V/gauss。当5V 电压供桥时,传感器满量程输出电压范围±30mV,DSP自带内部AD量程为0~3V,因此将仪用放大器参考电压设定为1.5V,放大倍数设置成50倍,即可达到AD满量程。利用磁原理,传感器HMC1052测量工件表面散射磁场法向分量Hp(y)沿坐标X-Y分量,通过计算、误差校正,由公式:Hp=√X2+Y2即可得到Hp(y)值。Hp(y)符号与测量基准方向Y的符号相同。图2为HMC1052传感器单轴调理电路,另一轴调理电路与图 2相似。

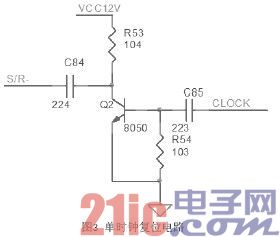

磁阻传感器在制造过程中,选定沿着薄膜长度方向为轴,当玻膜合金薄膜受到强磁场干扰时(大于20gauss)薄膜磁化极性会受到破坏,需要对传感器施加一个瞬态强磁场来恢复或保持传感器特性,这个过程只要DSP提供一个置位或复位脉冲CLOCK信号即可。图3为单时钟复位电路,其中CLOCK接DSP的一个 GPIO口,S/R-接HMC1052的8脚,相应HMC1052的第六脚接地。

1.2DSP与CPLD及相关外设通信

随着DSP芯片的工作时钟越来越高,指令的执行周期越来越短,而挂接在系统上的外设,如:按键、显示屏、蜂鸣器等,速度各不相同,且均相对DSP来说,速度较慢,DSP如果直接对这些片外模块进行控制,将会带来很大的时间开销。在本系统中,DSP对外设的控制经常需要用到种类较多的门电路、译码电路、时序电路等,为了节约PCB板的面积,增加系统设计的灵活性、可靠性,采用CPLD实现DSP的外围电路控制,能充分地利用CPLD中的资源,减少软件编程的复杂度,提高DSP的执行速度。这样,DSP对每一个外设都分配一个地址,CPLD通过DSP传过来的地址线、控制线和数据线来进行对相应外设的控制。对于按键类型的外设,当按键按下后,首先CPLD对按键进行消抖,CPLD得到按键值后,再通过中断通知DSP,DSP再通过总线来读取按键值。

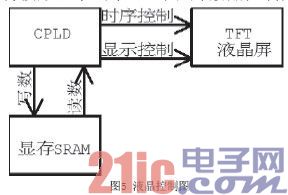

TMS320F28335 通过四位地址总线(XA[11:8])、数据总线(XD[11:0])、外部读写使能信号(RD、WR)、片选信号(CS)及I/O中断信号与CPLD相连,由这些信号连线完成DSP对CPLD内的相关寄存器或I/O的读写操作。挂接在CPLD上的所有外设DSP都可以通过地址线XA[8:11]来分配一个对应的地址,当在DSP中执行写指令:*(0x0400)=0x001时,地址总线XA[11:8]=0100B,数据线 XD[11:0]=0x001,同时控制线中CS、WR为低电平,RD为高电平,CPLD接收到总线电平后,进行地址锁存、数据译码等操作,即可对相应地址上分配的外设进行控制。CPLD与DSP的连接关系如图4所示。

1.3TFT真彩液晶屏

液晶屏分辨率为272×480,尺寸为4.3英寸。显示色彩为16位,RGB各占6位、5位、6位,采用3.3V电压供电。CPLD上外挂一片 16×256kB的SRAM作为显示屏的显存,存储一帧屏显的数据。CPLD将DSP总线上传来的数据,先存入显存,然后再从显存中读取出来,配合液晶屏驱动时序,在液晶屏上将波形显示出来。图5为液晶控制图。

2软件设计

本仪器所实现的主要功能有:漏磁信号采集处理、信号波形液晶显示、声音报警和按键功能设定。其中信号采集由DSP内部AD中断完成,只需要设置好相关寄存器即可。由于波形显示和声音报警是直接由DSP通过总线将命令发送到CPLD;而按键功能设定是:当按键按下后由CPLD通过中断来通知DSP,然后DSP 通过总线读取按键值,根据这些功能画出如图6、7的系统软件流程图,分别表示两块CPU各自内部程序流程。图6为信号波形显示和声音报警软件设计流程图,图7为按键功能设定流程图。

3总结

金属磁记忆作为一项新的无损检测技术,已在石油化工管道、发电站汽轮机、工程机械装备等领域得到越来越广泛的应用,采用DSP和CPLD组合设计的检测仪,不仅能保证高速的信号采集处理,而且利用了CPLD内部的硬件资源,大大简化了DSP访问外设时的时间开销,提高整个系统的执行速度。同时,CPLD预留了一定扩展接口,方便今后系统更新和升级。

评论