充分发挥PicoBlaze微控制器的优势

众多FPGA 应用均可通过使用简单的软核处理器来简化时序控制结构的生成,从而深受其益。

本文引用地址:https://www.eepw.com.cn/article/201610/308377.htm作者:Adam P. Taylor

e2v公司工程系统负责人

aptaylor@theiet.org

PicoBlaze 是一款结构紧凑的8 位软核微控制器,FPGA工程师可在其所选的赛灵思FPGA 中对其进行实例化。一旦实现,该处理器完全包含到仅使用逻辑Slice 和Block RAM 的FPGA 架构中;无需外部易失性和非易失性存储器。

由于其实现方案封装面积小,FPGA 才可能容纳多个PicoBlaze 实例化。每个实例化用于实现通常由状态机创建的控制结构。这样不仅能缩短开发时间,而且还可用标准化方法来控制结构生成。由于赛灵思FPGA结构潜在的高性能,PicoBlaze 实例化往往能够超越许多分离式8 位微控制器。

下面让我们看看如何在我们的设计中充分利用这款便捷的器件。

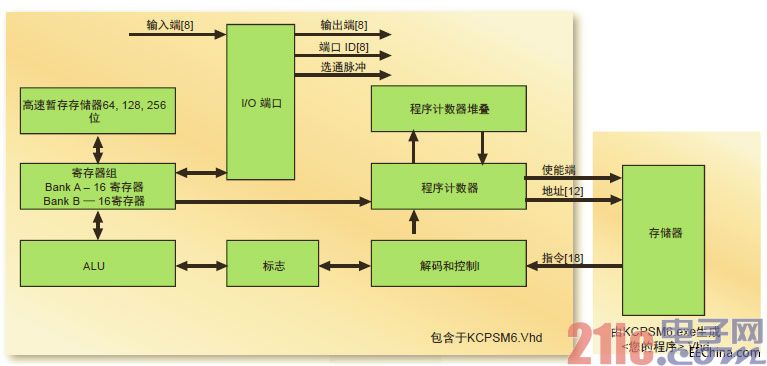

PICOBLAZE 架构

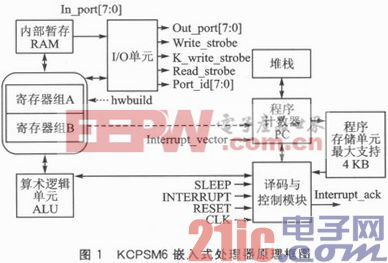

在使用这个处理器之前,首先让我们了解一下它的架构。PicoBlaze 是一款基于RISC 架构的非常简单的8 位微控制器(如图1 所示)。该控制器有一个12 位的地址端口,这意味着它可以处理多达4096 个存储器位置。

图1 – PicoBlaze架构,处理器(左)和存储器(右)

每个地址位置包括一个18 位指令,用以定义该处理器必须执行的操作。该处理器的输入输出可能通过两个8位端口(一个输入端口,一个输出端口)。该控制器还提供了一个8 位识别端口,可让多达256 个外设通过该端口进行读写。此外,该控制器还提

供一个64、128 或256 字节大小可选的高速暂存存储器。跟所有微处理器一样,PicoBlaze 包含一个算术逻辑单元并支持一个中断。有了这些功能,意味着该控制器能够为FPGA 设计工程师带来众多优势。

PicoBlaze 最重要的一个方面是它具有高度的确定性,这意味着所有指令都需要两个时钟周期才能执行完毕,中断服务最多需要四个时钟周期。( 您可以通过下载赛灵思用户指南,了解有关PicoBlaze 架构的更多详情。)

如何使用PICOBLAZE?

FPGA 应用通常需要结合并行和时序操作,其中数据流主要采用并行操作,而控制结构主要以时序结构实现,如状态机。(参见《赛灵思中国通信》第46 期,“ 如何在您的FPGA 中实现状态机”)。然而,复杂的控制结构如果以状态机实现,可能会变得

难以处理,不仅会延长验证时间,而且还会让开发周期的后期修改变得困难重重。复杂的状态机还需要花更多时间来开发,如果需要开发数个,那么花费时间就会相当长。

此外,您还可以使用PicoBlaze控制通过RS232、I2C 和SPI 接口的串行通信。事实上,您采用典型8位微处理器实现的任何方案均可在PicoBlaze 中实现, 而且具有更高的性能。工程师们已经用PicoBlaze 在控制系统中实现PID 控制器。他们结合使用PicoBlaze 与I2C、SPI 或并行DAC 来创建方形、锯齿和三角形以及更复杂的正弦/ 余弦等各种参考波形(使用移位加CORDIC 算法)。在您的FPGA 中实例化PicoBlaze 微控制器来实现这些时序功能,不仅可缩短开发时间,而且还允许在开发周期的

后期阶段进行简单的修改。当然,作为软核,PicoBlaze 还有助于解决过时问题,而且在您开发ASM 模块时还支持设计重用。

首个PICOBLAZE 实例化

遵循以下几个简单步骤,您就可以在您的设计中快速实现PicoBlaze。首先,确保您将用于目标器件中的微控制器是最新版本。您可从赛灵思PicoBlaze 下载区下载这些微控制器产品,这里既提供支持最新7 系列器件的版本,又提供能与旧版Spartan®-3

和Virtex®-4 器件协同使用的微控制器版本。

当下载了正确的处理器版本后,将这些文件解压到您的工作目录下并确保您能读取“read-me”文件,同时根据需要密切关注路径的设置以及赛灵思的环境变量。在您的工作目录中, 您将注意到以下文件或应用,以及有用的read-me 文件、许可证文件和用户指南。

• KCPSM6.Vhd: 这是一个真正的PicoBlaze 源代码。

• KCPSM6.exe :这是一个汇编程序,您可运用其生成所需的机器码和存储器文件。

• ROM_Form.vhd :这是一个可执行汇编程序,使用该文件可以生成VHDL 文件,您创建的程序将存储在这里。

• KCPSM6_design_template vhd :这是一个PicoBlaze 处理器模板实例。

• All_kcpsm6_syntax.psm :这个文件是关于所有汇编程序命令和语法的定义。

对于我们的实例设计,如果你不想将PicoBlaze 及其程序存储器添加到现有项目中,那么最后一步您应在我们能实例化PicoBlaze 及其程序存储器的ISE® 设计套件中创建一个新的项目。

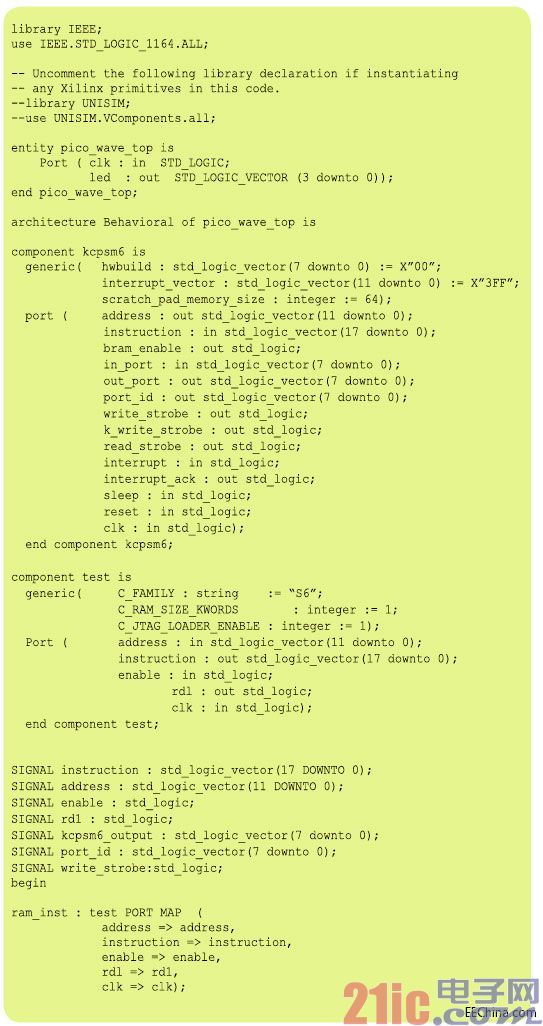

一旦完成上述步骤,我们就准备开始在我们的应用中创建PicoBlaze处理器。在此最简单的层面上,您只需在您的设计中声明两个组件:一个是处理器本身,另一个是程序存储器,如图1 所示 ( 处理器位于左侧方框中,存储器位于右侧方框中,用以提供上下文环境)。当然,如果您需要实现一个以上的实例化,那么您应该提供若干个存储器组件,用于存储不同的程序。然而,首先需要我们做的是了解典型项目的开发流程。

开发流程

创建首个PicoBlaze 实例其实很简单。第一步,使用Notepad++ 之类的编辑器创建一个空白的文本文件。该文件应该具备一个 .PSM 的文件扩展名,比如像“test.psm”这样的。您可以用PicoBlaze 汇编程序对微控制器进行编程。

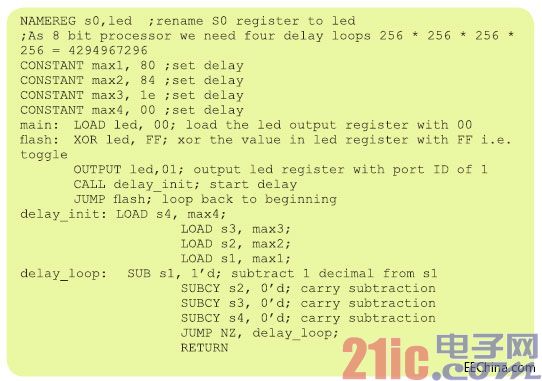

赛灵思在All_kcpsm6_ syntax.psm 文件中对该语法进行了详细介绍,您可以自行下载。无论怎样,这个语法很容易理解和掌握。图2 是汇编程序代码片段的示例,这是一个简单程序,用以闪存运行频率为2Hz、时钟频率为 40MHz 的LED。

图2 – 用于项目闪存LED的汇编程序代码片段

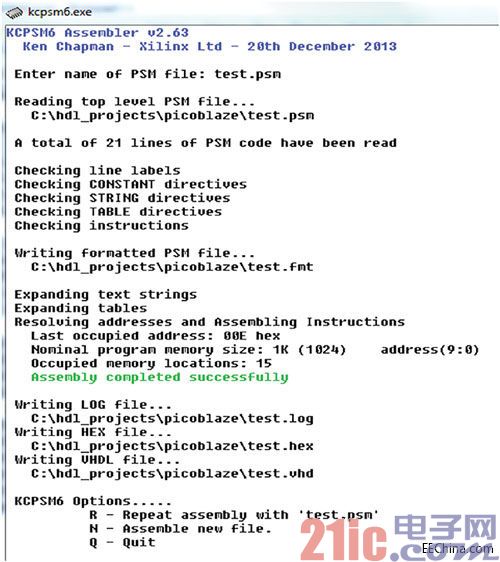

一旦您对自己的汇编程序感到满意后,就可以进行下一步:通过您下载的汇编程序可执行文件运行该程序。这样将会生成一个存储器文件 (您的FPGA 中会用到的VHDL)、一个日志文件和一个十六进制文件,我们将在后文介绍它们的用途。图3 显示了针对上述代码片段所运行的汇编程序流程。一旦运行汇编程序,您现在就能够在您的FPGA 内实例化PicoBlaze。

图3 –使用KCPSM6汇编程序生成存储器文件

您现在拥有两个所需的VHDL文件:KCPSM6.vhd 和由汇编程序创建的包含您的应用的VHDL 文件( 在本例中为test.vhd)。第二步:

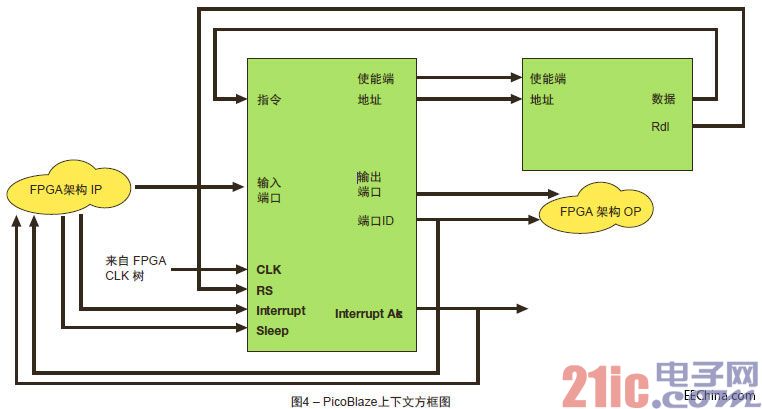

在您的VHDL 设计中声明两个组件(KCPSM6 和Memory) 并对他们进行实例化(如图4 所示)。在图5 所示的代码片段中可以看到这个简单的VHDL 示例。这个VHDL 示例实现的PicoBlaz 可以将LED 闪存到LX9Spartan® 开发板上。

图4 – PicoBlaze上下文方框图

图5 –将LED闪存到LX9 Spartan开发板上的PicoBlaze的代码片段

仿真与验证

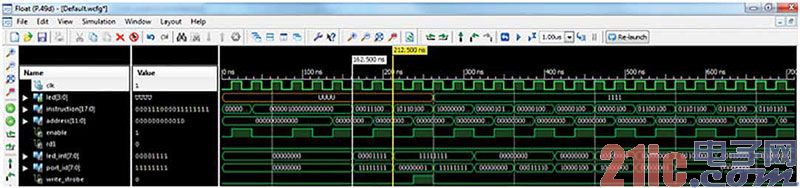

一旦您在应用中完成了设计文件的实例化,您肯定希望能在综合和实现之前在仿真环境中验证一下该系统或模块的性能。由于PicoBlaze 使用的是逻辑Slice 和 Block RAM,所以您在Mentor Graphics 的Mod-elSim 或赛灵思ISE 中的ISim ( 如果您是在

Vivado® 设计套件中的Xsim 中实现您的PicoBlaze,也可使用Xsim) 等程序中进行仿真就极其简单。

由于Block RAM 包含有针对您程序的指令,所以仿真工作自然就简单。基本上,您只需要提供一个时钟以及实例化要求的其他输入输出。图6 显示了在ISim 中进行的PicoBlaze仿真结果,以及指令加载之间的两个时钟周期。

图6 – ISim仿真结果

图6 – ISim仿真结果

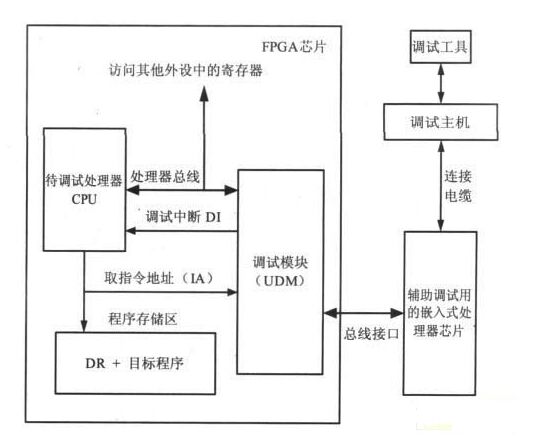

升级您的程序

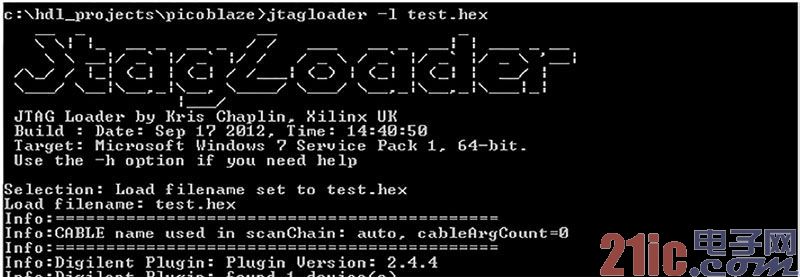

在FPGA( 以及比特文件) 中内置PicoBlaze 的最大优势之一就是在FPGA 配置完成后PicoBlaze 开始直接在其RAM 中运行程序。然而,在某些情况下,您可能需要修改该处理器核正在执行的程序。虽然根据设计余下部分的复杂程度,您可能会重新运行Implementation 阶段(包括更新了的存储器文件),但这会非常耗时,尤其是您只在实验室里尝试各种可能的情况下。因此,在重新运行Implementation 阶段之前可以用JTAGloader 更新处理器 核的程序存储器,来调试你的软件程序。其中JTAG loader 也能通过下载获得。

在使用JTAG loader 之前,首先需要在您的设计设置中启用该加载程序。在一个程序存储器的实例化中使用通用C_JTAG_LOAD-ER_ENABLE: integer := 1 。注意您一次只能为您设计中的一个内存实例设置该参数。

在您的设计中启用该程序后,您必须从JTAG_loader 目录中选择和你的操作系统匹配的版本并将其复制到您的工作目录下 ( 即十六进制文件所在位置)。现在您可以打开一个命令窗口并导航到您的工作目录下,然后使用以下命令。

jtagloader –l

注意:我已经我的操作系统重新命名为可执行文件版本,即jtagloader.exe。

当您在您的最新PSM 文件上运行汇编程序时,此项操作将下载所创建的十六进制文件,结果如图7 所示。下载该文件后,您将注意到JTAGloader 会停止处理器执行并在释放处理器复位之前下载新的程序到存储器中,此时处理器开始运行新的程序。

一旦您对PSM 文件的更新行为感到满意,您就可以重新运行实现方案和比特文件生成,从而确保下次该器件经过配置,能够执行更新的程序。

评论