流水线ADC设计中的数字校淮算法与实现

摘要:数字校准是高速高精度流水线ADC设计中的关键技术之一。文章提出了一种可通过校准控制生成测试信号,自动计算权重来对流水线ADC中电容失配进行误差补偿的技术。该技术能有效地减小增益有限、电荷注入等非理想因素的影响,使校准输出后的数据拥有更高的准确度,提高了系统的线性度。

本文引用地址:https://www.eepw.com.cn/article/201610/306773.htm0 引言

模数转换器(ADC)是联系模拟世界与数字系统的关键环节。在不同的应用领域,对ADC的性能需求也不同。在近年的国际固态电路大会(ISSCC)上发表的相当多的关于高速高精度ADC的文章表明,流水线ADC已经成为研究热点。流水线ADC采用流水作业的方式,在采样速率和转换精度上较其它类型的ADC有较大的优势,但是流水线ADC中存在电容失配、比较器失调、非理想运放、工艺误差等非理想因素,当流水线ADC的转换精度达到12位以上时,这些非理想因素对其性能有较大影响。传统的模拟电路校准技术已无法满足高精度的要求,而近年来随着数字系统的高速发展,采用数字方式对误差进行校准已经成为大趋势。数字校准技术得到了越来越广泛的应用。

本文针对14位250MSPS流水线ADC中的数字校准技术进行了研究,并提出了相应的实现方案。本方案无需修改各级MDAC模拟电路,只需在比较器输入端添加一个多位选择器即可实现,可满足流水线ADC对高线性度、高精度的要求,简单可靠、易于实现。

1 流水线ADC基本结构及误差源

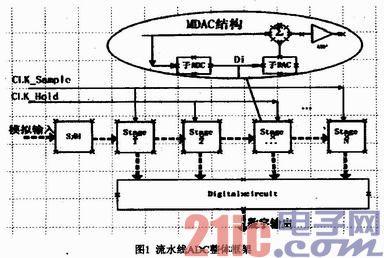

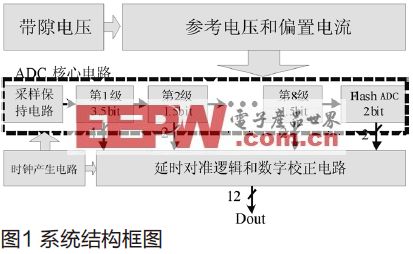

流水线ADC工作在两相不重叠时钟(采样时钟和保持时钟)下,用以控制各级MDAC在采样阶段和放大阶段之间交替工作。各级MDAC包含低精度子ADC、子DAC、减法电路及增益电路。在采样时钟控制下,输入的模拟信号被输送到子ADC的比较器上,产生多位数字输出Di及相应的模拟估计值,减法电路实现输入Vin与估计值的差值,所得余量电压在放大阶段通过增益放大电路放大,其模拟输出作为下一级MDAC的模拟输入。流水线ADC整体框架如图1所示。

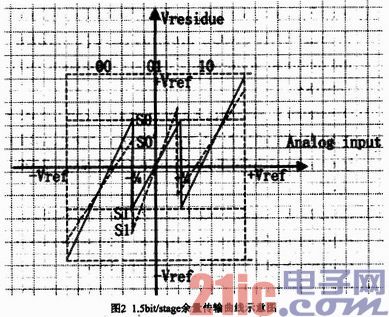

常见的流水线MDAC结构主要有1bit/stage、1.5bit/stage、3bit/stage和多bit/stage 4种,本文采用的是1.5bit/stage或其相似的结构。1.5bit/stage结构与其他结构相比,拥有可以容忍更大的失调电压等许多优点,其余量传输曲线如图2所示,实线为理想情况,虚线表示实际曲线。

从图2可以看出,实际余量传输曲线与理想余量传输曲线发生了偏移,这是由诸多的非理想因素造成的。如比较器失调误差可使余量曲线阈值电压左右偏移,运放的有限增益使得余量曲线斜率不等于2,电容失配导致余量曲线中曲线斜率改变和左右偏移,开关沟道电荷注入误差引起余量曲线整体上下偏移等。这些非理想因素影响流水线各级MDAC的转换精度,且逐级放大,最终导致失调或失码误差。

2 校准原理及实现方案

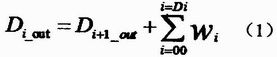

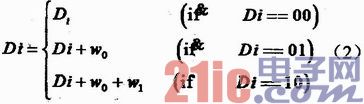

观察图2可以看出,由于各种非理想效应的存在,传输曲线在跳变点处的实际权重与理想权重产生偏差,理想的权重表现在余量曲线上为S0-S1,而实际的权重为S0'-S1',权重的差值导致数字输出产生相应的失调或失码误差。本文采用的校准思路是基于计算跳变点实际高度的测量。在1.5bitMDAC里,其数字输出有00、01、10三种情况,对应两个权重wi(i=0,1)。本级的总的数字输出是后级数字输出与本级数字码对应的权重累加之和。如式(1)所示,Di_out为第i级到第N级产生的总的数字输出,Di为第i级生成的数字输出。

此技术在操作过程中有“权重测量”和“数据转换”两种状态。权重测量包含两个步骤,在采样时钟控制下强制第i级MDAC接入比较器阈值电Vi_in=-1/4Vref,且令Di=00,产生的余量电压Vres1'经过后级MDAC生成的数字码为S0'。在保持时钟控制下强制第i级MDAC接入比较器阈值电Vi_in=-1/4Vref且令Di=01,产生的余量电压Vres2'经过后MDAC生成的数字码为S1'。理想情况下Vres1'-Vres2'=1/2*Vref,而实际情况下Vres1’-Vres2’=(1/2*Vref+△ε),即两者之间存在一差值电压△ε。对应的数字输出差值D(△ε)=(S0’-S1’)-D(1/2*Vref),D(1/2*Vref)已知,(S0’-S1’)可由计算得出,故可得出第i级MDAC对应的D(△εi)。我们可通过重复1024次再求平均值的方法来提高精度。因此我们得到实际的数据变换数字输出如下:

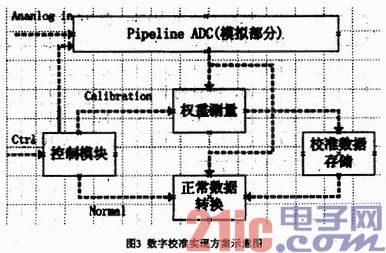

本文具体的实现方案如图3所示。数字电路实现由寄存器、加法器、移位器等组成,包含控制模块、权重测量、正常数据转换及用于存储器校准数据的寄存器四部分。系统由控制模块进行控制,可工作在两个工作模式下。在Calibration模式下控制模块发出测试信号输入到ADC模拟部分,生成的数字输出经由权重测量模块测得误差系数,存储到寄存器中。在Normal模式下进行正常的数字转换时调用这些系数来进行数字校准,得到经过校准后的较精确的数字输出。

3 实验结果与分析

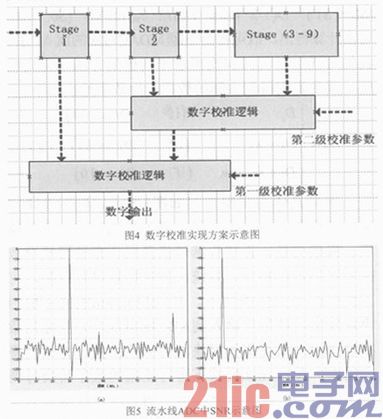

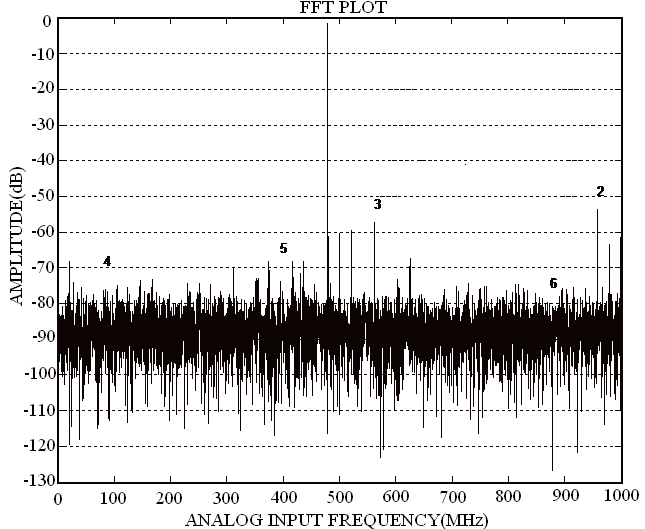

在ADC数字校准算法实现过程中,流水线ADC采用3.5bit+2.5bit(溢出)+1.5bit+1.5bit(溢出+4级)1.5bit+3bit flash 14位九级结构的MDAC,如图4所示。在进行校准时,前级实际权重的获得需要使用已经过校准的后级进行估算,在对第i级进行校准时,需要其后级已经过校准,可以看做满足线性度的理想ADC,因此整个校准从后向前逐级进行。本研究先校准第二级MDAC,然后再校准第一级MDAC,对两级MDAC共7bit2拄行数字校准,最终得到校准后的数据。校准前和校准后的ADC的SNR特性曲线如图5所示。

由图5(a)、图5(b)可以看出,校准前ADC电容失配值设置为1%,比较器失调为1%,在200MHZ的采样频率下,对一个正弦信号采样,校准前流水线ADC的SNR受谐波失真影响,为78.01dB,校准后SNR上升到81.21dB,所有的谐波都下降到-90dB以下。校准后总谐波失真由-65.05 dB下降到-88.59dB。可见,通过数字校准后,整个流水线ADC的线性度有了很大的提高。

4 结论

本文研究了一种适用于流水线ADC的数字校准算法,并提出了相应的实现方案。本方案对模拟电路更改较少,而数字电路里无需使用数字校准中常用的乘法器或除法器。速度较快,简单可靠且容易实现。

评论