以高整合度混合信号单片机实现桥式Force Sensor应用设计

主要组件介绍

本文引用地址:https://www.eepw.com.cn/article/201603/287847.htm(1) HY16F184 : 数据处理与运算核心,主要负责执行运算四个Force sensor的扫描数据,并且透过I2C通讯做ADC Raw Data数据输出。

(2) ADC:HY16F184内建之模拟数字转换器,将Force sensor所测得的电压讯号,做模拟数字电压讯号转换。

(3) HDK Force Sensor :压力传感器,负责侦测压力大小,并且将压力转换为电压讯号。

3.2. 软件说明

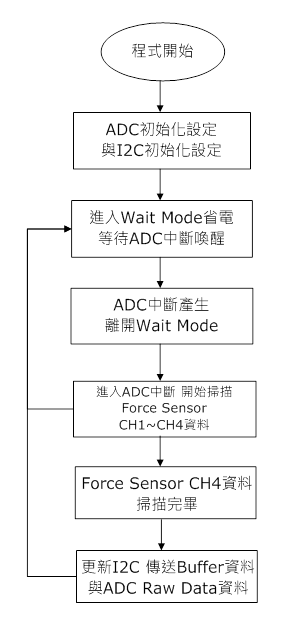

程序流程图 :

图7 Force sensor扫描流程图

4. 数据规格与总结

4.1. ADC Output Rate测量

在本文中,信道扫描的方式为每一个信道都扫描四次再取平均值,所以四个信道总共会需要扫描16次,在CPU频率设定为2MHz与ADC OSR设定为128的情况下(即ADC的数据输出率为2560sps),每次从CH1到CH4的扫描时间总共需要花费10ms,换算频率约为100Hz。在此条件下,如果要提升ADC的扫瞄速度,可选择提升ADC OSR设置,但是这可能会损失了分辨率,如果选择提升了CPU的工作频率,也可能会造成整体消耗功率过大,在此情况下,本文建议可使用移动平均法来做数据的平均与计算,使用此方式做扫描,可以在不提升CPU功耗与ADC频率的情况下,满足每个通道也为取四笔值取平均的条件,把ADC Output Rate速度从100Hz提升到192Hz。移动平均法的方法为,只有第一次扫描四信道的ADC Raw Data需要完整的扫描16次,之后各个信道的扫描只需要做一次扫描,再与前面三笔旧的数据做平均值计算,不断的递归更新数据。

4.2. 耗电流测量

在CPU频率设定为2MHz与ADC OSR设定为128的情况下,使用移动平均法可以得到的ADC Output Rate为192Hz,当CPU工作电压VDD=3V, VDDA=2.4V时候,在此情况下所测得到的耗电流约1.142mA,此为VDDA不接上HDK Force Sensor负载电路时候耗电流,如果在VDDA接上HDK Force Sensor负载时候的耗电流约为1.568mA。

4.3. 最大承受力

在ADC Gain=8,PGA=1的情况下,可以满足最大5kg秤重,使用者可以自行修改ADC的Gain值,以满足不同的应用。

4.4. ADC Raw Data与I2C通讯格式说明

I2C Slave Address:0x20

I2C Command:0x80

ADC Raw Data Format: S+Addr+0x80+rS+(Addr+1)+CH1Data_L+CH1Data_M+CH1Data_H+CH2Data_L+CH2Data_M+CH2Data_H+CH3Data_L+CH3Data_M+CH3Data_H+CH4Data_L+CH4Data_M+CH4Data_H+P

S: Star; Addr: Slave address; rS: repeat start; P: stop.

CH1,CH2,CH3,CH4: Force Sensor ADC Raw Data;

L: ADC Low byte; M: ADC Middle byte; H: ADC High byte;

每个信道数据(Chx)共8*3=24bit

Bit0,统一为旗标,Bit0=0b,代表为旧资料; Bit0=1b,代表为新资料;

使用者应该在Bit0=1b时,取得数据才有效.

Bit23,统一为Sign bit,

Bit23=0b,代表正数; Bit23=1b, 代表负数

评论