频率特性测试仪的设计

频率特性是一个网络性能最直观的反映。频率特性测试仪用于测量网络的幅频特性和相频特性,是根据扫频法的测量原理设计,是一种快速、简便、实时、动态、多参数、直观的测量仪器,可广泛应用于电子工程等领域。由于模拟式扫频仪价格昂贵,不能直接得到相频特性,更不能打印网络的频率响应曲线,给使用带来诸多不便。为此,设计了低频段数字式频率特性测试仪。该测试仪采用数字直接频率合成技术专用的集成电路AD985l产生扫频信号,以单片机和FPGA为控制核心,通过A/D和D/A转换器等接口电路,实现扫频信号频率的步进调整、数字显示及被测网络幅频特性与相频特性的数显等。该系统成本低廉,扫频范围较宽(10 Hz~1MHz),可方便地与打印机连接,实现频率特性曲线的打印。

2 多功能计数器设计方案

2.1 幅频和相频特性测量方案

方案1:利用公式H(s)=R(s)/E(s),以冲击函数为激励,则输出信号的拉氏变换与系统函数相等。但是产生性能很好的冲击函数比较困难,需要对采集的数据做FFT变换,需要占用大量的硬件和软件资源,且精度也受到限制。

方案2:扫频测试法。当系统在正弦信号的激励下,稳态时,响应信号与输入激励信号频率相同,其幅值比即为该频率的幅频响应值,而两者的相位差即为相频特性值。采用频率逐点步进的测试方法。无需对信号进行时域与频域的变换计算,通过对模拟量的测量与计算完成,且精度较高。

综上所述,选择方案2。

2.2 扫描信号产生方案

方案1:采用单片函数发生器。其频率可由外围电路控制。产生的信号频率稳定度低,抗干扰能力差,灵活性差。

方案2:采用数字锁相环频率合成技术。但锁相环本身是一个惰性环节,频率转换时间长,整个测试仪的反应速度就会很慢,而且带宽不高。

方案3:采用数字直接频率合成技术(DDFS)。以单片机和FPGA为控制核心,通过相位累加器的输出寻址波形存储器中的数据,以产生固定频率的正弦信号。该方案实现简单,频率稳定,抗干扰能力强。

综上分析,采用方案3。

2.3 幅度检测方案

方案1:采用二极管峰值检测电路。但是二极管的导通压降会带来较大误差,小信号测量精度不高,而且模拟电路易受到外部的影响,稳定性不高。

方案2:采用真有效值检测器件。该方法电路简单,精度高,稳定性高。

综上所述,采用方案2。

2.4 相位检测方案

方案1:相位电压转换法。采用低通滤波法和积分法。低通滤波法的滤波环节和精度不高;积分法精度较高,但是对积分电路和放电回路的要求很高。

方案2:计数法。两路信号经整形异或后,所得的脉冲占空比能反映相位差的大小,由此测得其相位差。采用多周期同步计数法,可使量化误差大大减小,精度很高。

综上所述,选取方案2。

3 系统总体设计

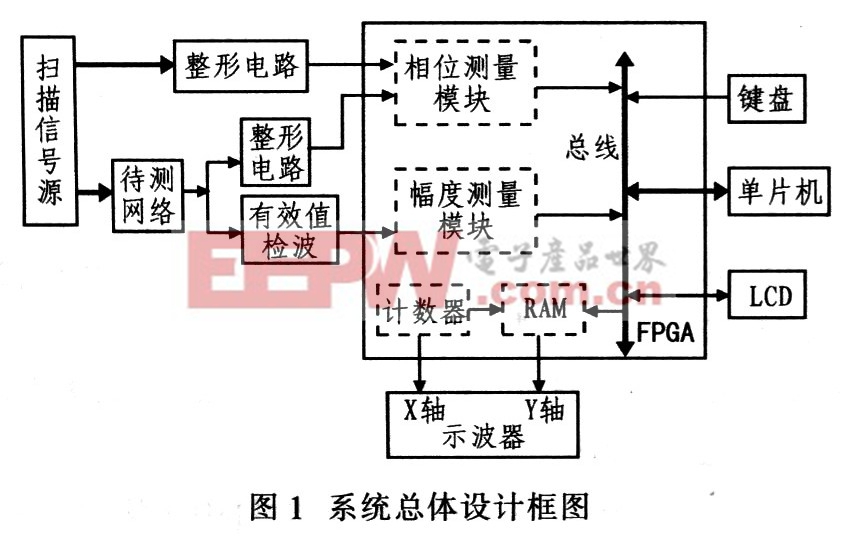

该系统以单片机和FPGA为控制核心,用DDFS技术产生频率扫描信号,采用真有效值检测器件AD637测量信号幅度。在FPGA中,采用高频脉冲计数的方法测量相位差,经过单片机运算,可得到100 Hz~100 kHz中任意频率的幅频特性和相频特性数据,实现在该频段的自动扫描,并在示波器上同时显示幅频和相频特性曲线。用键盘控制系统实现各种功能,并且在LCD同步显示相应的功能和数据,人机交互界面友好。图1给出系统总体设计框图。

4 理论分析与计算

4.1 扫频测试法理论依据

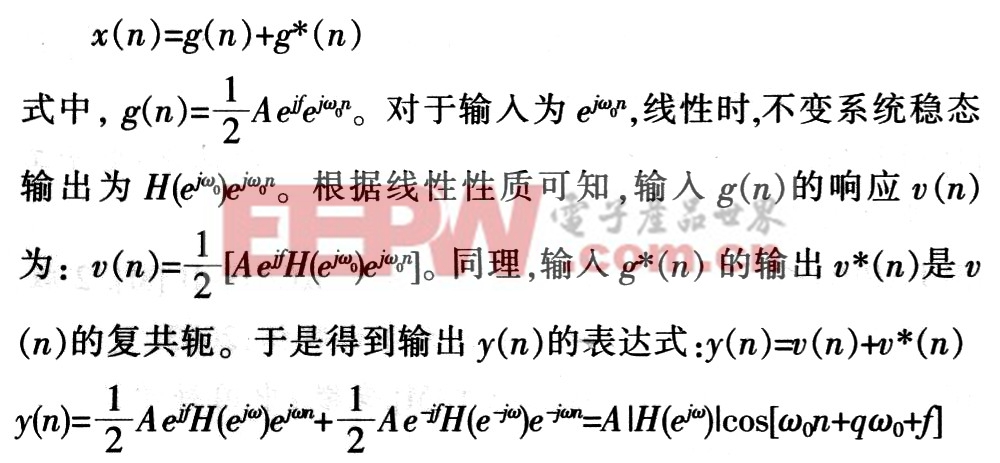

设频率响应为H(jω)的实系数线性时,不变系统在信号x(n)_Acos(ω0n+f)激励下的稳态输出为y(n)。利用三角恒等式,可将输入表示为2个复指数函数之和:

因此,输出信号和输入信号是频率相同的正弦波,仅有两点不同:第一,振幅被|H(ejω)|加权,即网络系统在ω=ω0的幅度函数值;第二,输出信号相对于输入信号有一个数量为q(ω0)的相位时延,即网络系统在ω=ω0的相位值。

4.2 DDS信号源

根据DDFS原理所产生的波形频率为:

![]()

式中fclk为基准频率,M为相位增量因子,N为累加器的位数。M取22,N取24。

为得到100 kHz的信号,而且在每个周期希望取到32个以上点,则累加器输出后级D/A转换需要至少3.2 MHz的速度,于是选取建立时间为30 ns、10位的DAC900,不仅满足了对D/A转换速度的要求,而且具有10位数据线,减少了D/A转换中固有的量化误差。fclk取40MHz,频率的最小步进:

![]()

评论