高性能手持示波表低功耗设计中的关键技术

1、引言

本文引用地址:https://www.eepw.com.cn/article/195794.htm手持式示波表由于便携性及可由电池供电工作,逐渐被广泛的应用于现场测试,在应用场合逐步拓展的同时,对手持示波表的性能要求也在不断提高,这里主要是指要求高样率的ADC和高速存储;目前国内示波表产品实时采样率主要是250MSaps以下,尚无高于500MSaps产品出现,除了受器件成本限制外,另一个重要原因是由于高速采样率带来采集系统(高速ADC及FPGA)工作频率大幅提高,直接导致系统功耗极大的增加,给系统散热、延长系统工作时间等带来极大的挑战。因此,在能够满足提高采样率的条件下实现低功耗设计是非常有意义的。

2、系统功耗组成

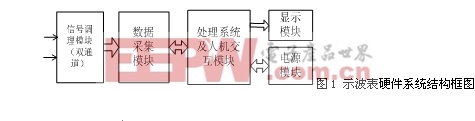

当前手持示波表硬件系统的主要结构如图1所示:

其中信号调理模块用于对被测信号的调理,这部分大多以衰减网络、运算放大器及控制继电器等构成;数据采集模块主要由高速ADC、FPGA及触发电路等构成;处理系统及人机交互模块等由处理器、存储器及输入输出结构等组成;显示模块主要是指液晶屏,当前流行的是真彩 LCD,示波表中大多采用320×240的分辨率;电源模块通常由开关电源IC实现,当然这里要求电源转换效率尽可能的高。通常高采样率示波表与低采样率示波表的关键差别在于数据采集模块的不同,数据采集模块中ADC采样率的提高,必然带来其功耗的增大,这也必然要求电源模块的输出功率增大,而其他模块相对于采样率的高低是独立的,其功耗相对差异较小,不会因为采样率的提高而有变化。

2.1 高速ADC与功耗

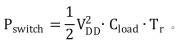

数据采集模块中的ADC决定了系统的采样率,采样速率不同,ADC的功耗差异是非常大的,如表1所示,其中AD9288与AT84AD004功耗相差有1.5W之多,而这仅仅是ADC之间的差异,实际上,根据CMOS集成电路平均动态功率消耗的经典公式:![]()

可知,当在电源电压 和负载电容 确定的情况下,工作频率 直接影响着系统功耗,采样率不同的ADC输出不同数据带宽的数据流,后端FPGA接收这些不同速率的数据流,其相应消耗的功耗因为工作 不同,而也有较大差异的,另外,考虑到电源效率也不可能是100%,这种功耗差异就会被放大,整机功耗差异也就会增大,所以决定着系统高采样率指标的高速ADC带来了一系列的功耗提升,对系统的整体功耗起着非常关键的影响。

2.2 工作状态与功耗

在设计高采样率示波表之前明确其中的高采样率应用需求场合,以及示波表的大多数的工作使用状态,对于系统方案的具体实施是非常重要的。示波表处于不同的工作状态,对其内部的采集系统要求是不同的。

(1),高采样率示波表较相对低采样率的示波表而言,其高的采样率仅仅用在少部分的高速时基档位下。比如,某500MSaps采样率的示波表,时基档位从5s/div~5ns/div,一共 27个档位,其中仅7个时基档位对应于最高速500MSaps采样率,此时要求ADC工作在最高采样状态下,而慢速时基档位则对应于低速采样率,此时的高速ADC具有的高采样率是不必要的;显然两种采样状态下,ADC的功耗差异会非常大的,应该合理的利用这种采样率的动态差异,根据时基档位动态的调整ADC的采样时钟,达到在低速时基档位降低系统功耗的目的。

(2)通道的工作状态影响系统功耗,用户大多数时候仅仅使用示波表的一个通道进行测量而关闭另一个通道,此时,如果将对应通道的采样ADC设置为休眠,是非常有利于减小功耗的;另外值得注意的是一般示波表中每个信号调理通道消耗约1W,触发通道等消耗约0.5W,单通道工作的时候休眠另一个通道或关闭其电源,也将减小可观的功耗;另外,用户使用示波表会经常对采集后的波形数据进行观察和分析等,此时示波表工作在停止状态,可将ADC完全休眠并关闭通道部分电源等,这会极大的降低不必要的功耗。

3、实现方案对比

某型号高采样率手持示波表要求双通道,每通道500MSaps,分辨率8bit,这里给出两套数据采集方案进行对比分析。

方案一:单片高速ADC直接实现。这里可选AT84AD004,是双通道500MSaps的高速ADC,要求输入500MHz PECL电平的采样时钟,通常这种高速时钟不能由FPGA提供,需选用专用时钟器件;AT84AD004内部两个通道可以独立控制是否休眠,一定程度上达到节省功耗的目的; 对于这类高速的ADC,其时钟方案实现的灵活性不高,采样时钟频率通常固定,不易动态更改。

评论