图像采集压缩和高清分析并行处理的硬件系统设计

摘要:将DSP与FPGA结合,设计一种对CMOS图像传感器进行图像采集和处理的硬件系统。该系统能够在硬件层面把图像分路处理,一路直接压缩后传输,另一路循环存储到多帧高清图像存储区,便于软件分析,较好地解决了传输带宽不足与智能监控需要高分辨率图像进行分析处理的矛盾需求。该系统具有高清图像实时采集处理的优点和硬件平台通用性,可用不同软件实现不同的图像分析处理。

本文引用地址:https://www.eepw.com.cn/article/195186.htm关键词:FPGA;DSP图像采集;图像处理;分路处理

0 引言

随着科学技术的发展和社会发展应用需求,人们对视频图像采集处理高清化,传输实时化和控制智能化的要求越来越高。高清视频图像在军事、科研、安防、工业生产、医疗卫生等领域得到了更为广泛的应用。

特别在安防行业,现有系统由于技术、成本和传输距离的原因,传输带宽都不高,直接实时传输高清视频图像难以实现,但是某些关键时刻或者特殊场景却需要高清晰度、高分辨率的图像进行细节的分析处理,便于智能化的应用。本文为了解决这一个矛盾的需求,提出了在视频监控系统的前端——图像采集和处理将采集到的原始高清图像数据分成两路同时进行处理的思想:一路按照传统的处理方法压缩处理转为标清视频流传输,实现监控的实时化;另一路数据由外部扩展SDRAM缓存,DSP实时读取缓存数据进行智能分析处理,根据分析处理结果决定是否传输高清图像或者结果。基于不同处理芯片在图像处理各层次应用有不同的针对性,合理分配硬件资源及算法,能够显著提高系统整体性能。本文采用FPGA+DSP技术实现高清图像采集和处理,并在硬件层面将数据分路处理。

1 系统结构及原理

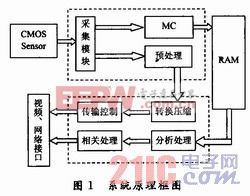

本文设计的硬件系统,就是利用FPGA和DSP对高分辨率CMOS数字图像传感器OV5642进行图像采集和处理。系统完成对 FPGA,DSP和OV5642芯片进行初始化。FPGA对OV5642进行全分辨率的数据采集。FPGA将采集到的图像数据成两路处理,一路直接原始高清数据传输外部SDRAM缓存,由DSP读取缓存数据进行智能分析处理;另一路由FPGA进行硬件预处理,将原始高清图像转换为合适的分辨率,送到DSP 片内进行格式转换、压缩等处理后传输到外部接口。DSP根据分析处理结果和设置阈值条件,决定是否对高清图像数据进行传输。需要传输的图像帧融入数据流中传输。外部扩展的输出接口可以将经过系统处理的数据流传输到本地监控或者远程监控。系统原理框图如图1所示。

在高清实时图像采集处理中,图像采集的速度高,低层的预处理中要处理的数据量大,对处理速度要求高,但运算结构相对比较简单,适合用兼顾速度及灵活性的 FPGA进行硬件实现。高层的处理算法的特点是处理的数据量较低层算法少,但算法的结构复杂,适合用运算速度高、寻址方式灵活、通信机制强的DSP芯片来实现。DSP+FPGA架构的最大特点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率,同时其开发周期短,系统易于维护和升级,适合于实时视频图像处理。

在本设计中充分考虑到FPGA和DSP在图像采集处理各层次应用有着不同的优势,采用FPGA+DSP结构,通过合理的硬件资源分配及算法处理,实现了高清图像采集和实时处理。在FPGA内设计采集模块和预处理模块,充分利用FPGA时钟频率高,内部延时小,运行速度快,全部控制逻辑由硬件完成的特点,主要完成图像数据采集、数据分路和图像缩放预处理。通过FPGA内模块间协调,在硬件层面完成数据的分路。在

DSP内则是利用DSP运算速度快、寻址方式灵活、通信机制强大等特点,主要完成系统配置、图像格式转化、压缩处理以及图像的智能分析处理、传输接口配置等。

2 系统硬件设计

2.1 图像采集模块设计

图像采集模块主要包括传感器工作模式配置、图像采集控制和数据传输。整个模块的功能示意图如图2所示。FPGA片内模拟I2C控制器,将COMS图像传感器OV5642初始化。OV5642在外部时钟VXCLK作用下,输出Bayer RGB格式图像数据和同步时钟。FPGA内部设计的采集控制器在PCLK,HREF,VSYNC同步时钟作用下,产生相应控制读写信号,进行数据传输采集。

评论