测试嵌入式存储器的标准技术

随着SoC设计向存储器比例大于逻辑部分比例的方向发展,高质量的存储器测试策略显得尤为重要。存储器内置自测试(BIST)技术以合理的面积开销来对单个嵌入式存储器进行彻底的测试,可提高DPM、产品质量及良品率,因而正成为测试嵌入式存储器的标准技术。

本文引用地址:https://www.eepw.com.cn/article/193870.htm半导体行业向纳米技术的转移已经引起人们对制造测试工艺的重新思考。由于早先的良品率要大大低于采用更大规模工艺技术所获得 的良品率,并且新缺陷类型正在不断出现,故半导体制造测试将在保证产品质量方面扮演着更加重要的角色。在传统上,测试技术主要集中在设计的逻辑部分上,但 统计资料显示:今天的设计已经普遍含有50%的嵌入式存储器,且这部分的比例预计在未来几年中还会加大。很明显,为实现全面的系统级芯片(SoC)测试, 必须制定一种高质量的存储器测试策略。

存储器紧凑的结构特征使其更容易受到各类缺陷的影响。存储器阵列工作模式本质上主要是模拟的,来自存储器件的弱信号被放大 到适当的驱动强度,且存储器单元的信号传输只涉及到很少的电荷。所有这些设计特点都使存储器阵列更容易受到错综复杂的制造缺陷的影响。而紧密的存储器阵列 封装造成了这样一种情况,即相邻单元的状态在存在缺陷的情况下可能会发生误操作,因此某些缺陷可能只在特定的数据模式下才会暴露。此外,这些缺陷类型很多 是具有时间相关性的,因此只有在正常工作频率下才会被发现。

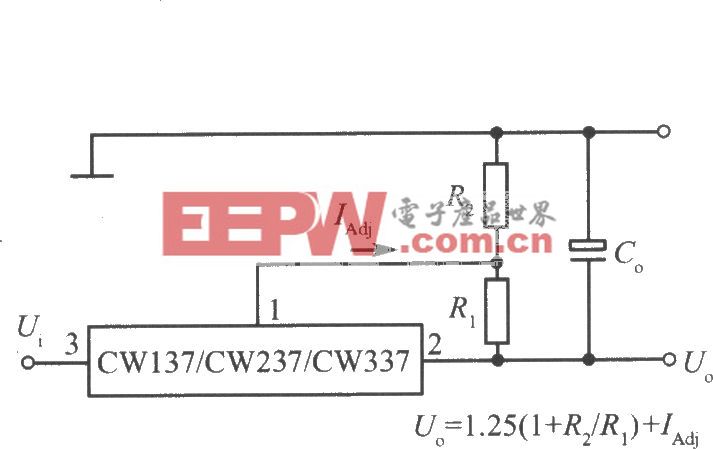

存储器内置自测试(BIST)是SoC设计中用来测试嵌入式存储器的标准技术,它以合理的面积开销来对单个嵌入式存储器进行彻底的测试。最常见的存储器BIST类型包括可完成三项基本操作的有限状态机(FSM): 将测试模版(pattern)写入存储器、读回这些模版并将其与预期的结果进行比较。为对嵌入式存储器进行存取,存储器BIST一般将测试多路复用器插入 到地址、数据及控制线路中。存储器BIST完成的最普遍测试类型为“March”型算法,该算法可检测出绝大多数常见的存储器缺陷,包括粘着、寻址出错及 耦合问题等。

目前一组“March”算法已被开发出,并在大多数情况下构成了一个高效嵌入式存储器测试方法集的核心。但随着SoC设计 向纳米技术转移,制造商们会关心不断增加的、逃过这些测试的存储器缺陷数量。基于这一原因,存储器测试工程师们目前正在继续开发新的“March”算法变 体。随着存储器尺寸的日趋缩小以及新型存储器体系结构的开发,这种趋势肯定还会继续。毋庸置疑,存储器BIST工具将提供足够的灵活性来跟上这一发展趋势。

全速(at-speed)测试的新挑战

如今很多公司发现,所有嵌入式存储器的全速测试均要求能保持在一种可接受的“每百万片缺陷数”(DPM)水平上,也只有通过 全速测试,厂商们才能相信存储器在终端应用的常规运行中会正确工作。当嵌入式存储器工作在较高频率上时,许多存储器BIST结构的实现可能并不是全速运 行。幸运的是,当前在存储器BIST技术上所取得的进步允许使用全速测试算法,即使在存储器工作频率接近1GHz时。

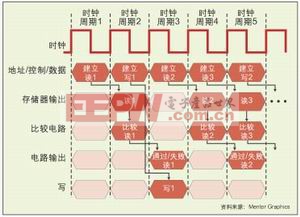

实现全速存储器BIST操作的一个巨大进步是使用测试流水线,它能提供以下几个关键优势:首先人们需要考虑由存储器 BIST完成的三个主要步骤即,写入测试模版、读取该模版然后再将其与预期的结果进行比较。流水线使得这三个步骤可以并行进行。在写入新的数据的同时,以 前读取的结果被记录,且在一个时钟周期内还可对以前读取结果进行比较操作,这能将测试时间缩短三分之二,而且,对存储器的高速操作也能发现那些在非流水线 处理中所无法察觉的缺陷。

流水线存储器BIST架构也使其在测试极高速度存储器时易于满足时序要求,增加的注册意味着可缩短电路测试中的关键路径长度。这些时间上的节省,也意味着全速测试提供额外的质量保证可适用于更大批量的嵌入式存储器测试。

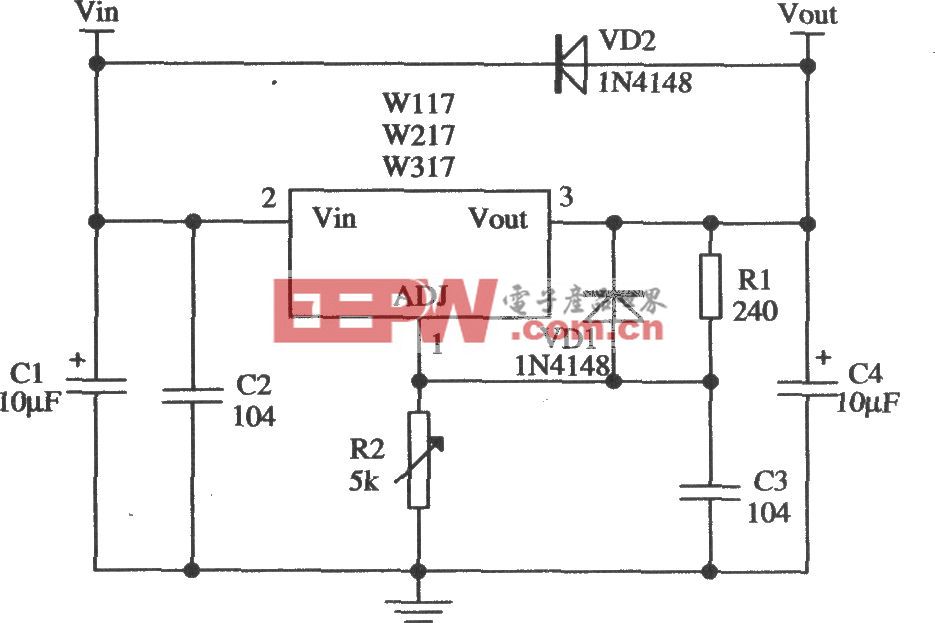

全速测试的应用因嵌入式测试多路复用器的使用而变得更为容易实现,拥有直接设计进存储器中的多路复用器,意味着所增加的 BIST结构将只对系统线路延时产生最小的影响;此外,嵌入式存储器供应商还可对嵌入式测试多路复用器进行优化以进一步减少延时影响。重要的是,存储器 BIST应用工具以这些嵌入式多路复用器来辨识存储器,从而无需手动修改网表即能对它们加以利用。

全速诊断

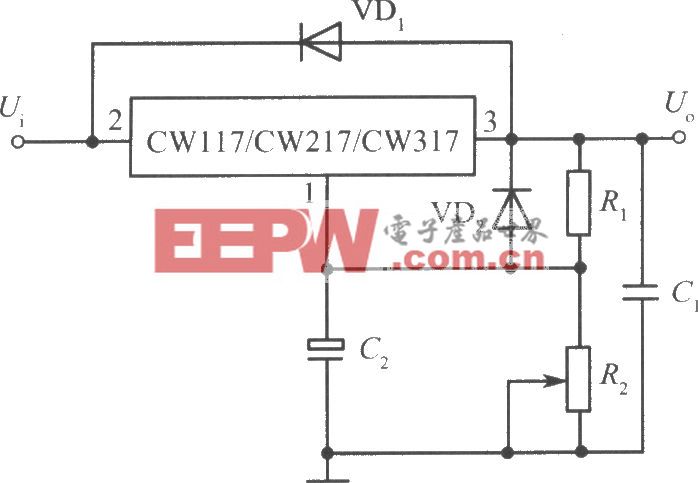

与确定哪些嵌入式存储器存在缺陷同样重要的是分析缺陷产生的原因,而将缺陷诊断电路包含进存储器BIST中正在纳米设计中变 得日益普遍。但许多存储器测试诊断电路目前还不能进行正确的全速测试,在存储器缺陷诊断中采用速度相对较慢的时钟来将缺陷数据输送给测试器就会暴露出这一 问题。如果存在多个缺陷,则BIST必须停止以等待缺陷数据输送给测试器。但如果BIST在数据输送完以后即简单地重新开始,则全速测试模型将被破坏,而 缺陷也就有可能被漏掉。为解决这一问题,存储器BIST必须能重启测试,以返回到以前的地址上并跳过那些已经报告的缺陷。这使得BIST能获得一次新的运 行启动,以确保诊断分析期间能将测试模版正确地应用到所有存储器单元上,并使其达到全速。

可实现March算法定制变体的灵活存储器BIST引擎加上增强的全速应用,为确保对具有数百个嵌入式存储器的SoC设计进行高质量的测试提供了一个坚实的基础。随着芯片设计向存储器多于逻辑单元的方向发展,存储器BIST将成为提高DPM、产品质量及良品率的主要功臣。

评论