基于SOPC的简易误码率测试仪设计技术

设备上电后进入模式选择,用户根据需要设定模式,确认后,mode_reg设置完毕。随后进入速率选择,设置时钟分频器的数值,用以设置代码发送速率。Control_reg提供了AM7968其他端口的设置。参数设置完毕后,设置好的代码就配合设定好的时钟频率,通过通信端口发送出去了。

需要特别说明的是循环代码的发送过程。因为,在其他模式下,数据自发送开始就一直在数据总线上有效,只要控制好数据的发送脉冲信号即可;而循环代码模式下,数据需要实时更新,且不能有遗漏和跳跃,因此特别设计了循环码发生模块。它以AM7968芯片的ACK信号作为循环代码递增的触发信号。这是因为ACK信号是AM7968在数据发送完毕后立即发送的反馈信号。所以利用这个信号,就很好地保证了循环代码的可靠性。

(2)接收端设计

如图3所示,芯片AM7969是信号的接收端。在用户设定了代码模式后,AM7969的控制寄存器被配置为相应模式。之后设置误码计算模式,并将误码计数器复位,且设置好对应的对照代码。

AM7969芯片中的锁相环时钟生成器(PLL clockgenerator),可以从接收到的数据流中分离出时钟信号和数据信号。

由于线路传输存在延时问题,会使AM7969分离的时钟相对于发送端AM7968的时钟滞后。对比较器两端的输入来说,出现了不同步的情况。如果AM7969也利用本地系统时钟,那么其接收到的数据就会紊乱。这种方法不可取。

本系统采取发送同步序列的方式来进行同步。在测量开始后,发送端发送同步序列。在10 ms内(此时间阈值可进行设置),如果接收端没有收到同步序列,则判定线路故障,无法正常测量;如果在时间阈值内收到同步序列,则立刻进入测试状态。例如,当发送代码A0后,接收端如果在时限内(时间阈值)收到信号,则进行比较,之后发送1个反馈信号Dstrb和1个数据A1,依此类推;如果接收端没有收到信号,则系统将认为是误码丢失,记为误码,同时自行发送1个伪Dstrb,继续测量。

3.2 显示模块设计

显示部分采用了Visionox公司的VGGl2864E―S002、128×64点阵的单色图形显示模块。该模块有以下特点:亮度高,对比度高,视角宽,响应速度快,温度范围宽,功耗低;8位并行数据接口,读、写操作时序;模块内藏64×64显示数据RAM(RAM中每位数据对应OLED屏上一个点的亮、暗状态);接口电路简单,使用方便。

本设计通过VHDL语言编写接口时序IP核控制器oled.VHD,使其作为Slave device连接到Avalon总线上,实现了数据显示功能。

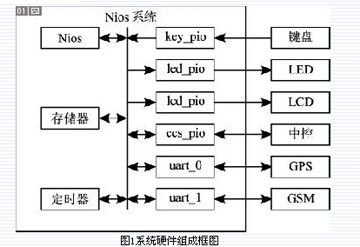

3.3 误码率测试仪的SOPC设计

图4为在SOPC Builder工作窗口中的该误码率测试仪的SOPC系统。

其中,cpu_0为主Nios II处理器,cfi_flash_bridge_O为Avalon三态桥用来连接Flash IP核控制器cfi_flash_O,sdram是SDRAM IP核控制器,timer_O是Nios II内部定时器,oled_O是OLED IP核控制器,pio_0是按键外部引脚,am7968_2_O和am7969_2_0分别是用VHDL语言编写的收发芯片AM7968和AM7969的1P核控制器。

评论