如何发现并解决FPGA设计中的时序问题

耗费数月精力做出的设计却无法满足时序要求,这确实非常令人伤心。然而,试图正确地对设计进行约束以保证满足时序要求的过程几乎同样令人费神。找到并确定时序约束本身通常也是非常令人头痛的问题。

本文引用地址:http://www.eepw.com.cn/article/192151.htm时序问题的恼人之处在于没有哪种方法能够解决所有类型的问题。由于客户对于和现场应用工程师共享源代码通常非常敏感,因此我们通常都是通过将工具的潜力发挥到极致来帮助客户解决其时序问题。当然好消息就是通过这种方法以及优化RTL代码,可以解决大多数时序问题。

但在深入探讨之前,我们首先需要对时序问题进行一点基本分析。这里的目标是首先排除明显的问题,如将时钟引脚置于器件的上部、在器件下部驱动数字时钟管理器(DCM),然后再在器件上部驱动全局缓冲(BUFG)。

有时,此类引脚布局会导致根本没有办法满足时序要求。通过察看时序报告中的延迟,通常可以发现这些明显的时序问题。在这些情况下,为了解决这些明显的问题,都需要利用底层规划工具“floorplanner”将造成问题的部分锁定在适当的位置。底层布局规划工具还可以帮助以可视的方式来理解时序问题。

用最新工具进行时序分析

假设问题并非这么明显,那么为了锁定问题所在,需要了解所使用的器件系列以及软件版本。通常,每种器件系列对应一种最优的软件版本。如Xilinx Virtex-4器件对应的最佳软件是ISE软件9.2i版,而对Virtex-5 FPGA则是ISE软件10.1版。

综合工具的版本也很重要,因此当采用最新的器件架构时,下载并使用最新版软件非常重要。软件开发几乎总是滞后于硬件功能,因此我不提倡使用旧版软件进行基于新器件的设计。

然而,有些客户由于担心新的和未知的软件缺陷而不愿意升级软件。但是,在使用最新的器件时,如果希望更好地处理时序挑战,强烈建议下载最新版软件。

拥有了最适用于目标器件系列的软件,还需要确定最佳的实现选项。可惜,并没有适用于所有情况的超级选项组合。对于设计实现工具来说,有成千上万种不同的实现选项组合。根据所使用的实现选项不同,时序分数(即所有存在错误的时序路径与时序要求的差异总和,以皮秒表示)也会有很大不同。

赛灵思的几款工具可帮助确定适用于特定设计的最佳实现选项。ISE软件现在包括两个工具:Xplorer以及最近发布的SmartXplorer。SmartXplorer可充分发挥多处理器优点,能够以不同选项组合运行多个实施实例。

SmartXplorer需要Linux支持,但使用非常容易。其命令行很简单:smartxplorer designname.edn -p xc5vlx110t-1ff1136.

只要用户约束文件(UCF)和网表约束文件(NCF)文件名相同,SmartXplorer会自动使用正确的选项。唯一需要做的是编辑主机列表文件。

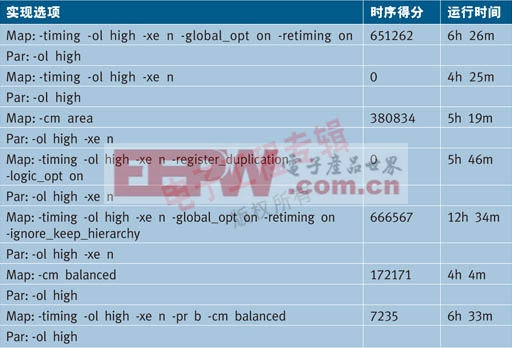

SmartXplorer可以通过SSH/rsh安全shell登录到其他机器。只需要在名为smartxplorer.hostlist的文件中将每台机器一行将机器名字添加进去就可以了。如果机器有两个处理器,请将机器列出两次。表1给出了SmartXplorer的一组结果。

表1:对基于Virtex-5 FPGA的设计SmartXplorer 10.1的一个例子。

PlanAhead软件也包括了与SmartXplorer类似的称为ExploreAhead的功能。ExploreAhead支持同时在多台Linux机器上分布式运行布局布线任务。所有这些工具的目的都是类似的:确定实现工具的最佳选项组合,以获得最好的时序得分。

请注意选项的不同组合对于时序得分和运行时间的巨大影响。仔细调整综合选项也非常重要。例如,在综合选项中关闭结构层次(hierarchy)通常会大大提高性能。综合过程中的约束条件好坏在满足时序方面的作用也很突出。

评论