雷达视频积累算法在FPGA上的实现

1 引 言

由于雷达所处的环境的复杂性,除了地物、云雨、鸟群等干扰外,还可能来自临近的雷达异步干扰、电台干扰等。所有的干扰,经过接收机进入信号处理机,虽然经过了中频信号的处理,但还可能有残余。因此,为了得到更好的检测性能,在检测前进行一次视频积累是非常必要的。

虽然视频积累的效果不如相参积累,但是视频积累的工程实现比较简单,对雷达的收发系统没有严格的相参性要求,且对大多数运动目标来讲其回波的起伏将明显破坏相邻回波信号的相位相参性,因此在许多实际工程应用场合还是采用视频积累。

在雷达视频积累算法的工程实现过程中,需要雷达信号处理器具有较快的实时性,并且对信号处理器的稳定性、体积、功耗等也有严格的要求。近年来随着FPGA技术的快速发展,为我们提供了一种更好的解决这一问题的途径。由于FPGA本身所具备的并行结构的算术结构,使得FPGA特别适合用作高性能的数据通路处理器。利用FPGA实现雷达视频积累算法具有实时强,硬件系统体积小结构灵活,适于模块化设计,开发期短,并且支持在线可编程,使系统具有较强的通用性可扩展性等优点。本文以此为出发点,提出并讨论一种利用FPGA技术实现雷达视频积累的方法。

2 系统的硬件结构

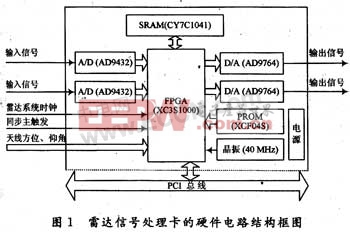

在具体实现过程中主要采用一块基于FPGA的芯达信号处理卡,既可以采集来自雷达接收机的中频、视频信号并对其进行数字信号处理,又可以自身模拟产生雷达中频、视频信号进行数字信号处理或不处理直接送往雷达信号处理机。雷达信号处理卡的硬件电路结构框图如图1所示。

FPGA采用的是Xilinx公司的100万门FPGA芯片XC3S1000,其配置芯片为Xilinx公司的1 Mb容量PROM芯片XC18V01,以主动串行方式对FPGA进行上电配置。AD,DA分别为ADI公司12位高速模数转换芯片AD9432与14位高速数模转换芯片AD9764SRAM采用Cypress公司的256 k×16 b SRAM芯片CYTC1041。

设计中利用FPGA实现32 b/33 MHz的PCI接口逻辑,进行实时信号采集和传输控制。由于FPGA具有层次化的存储器系统,其基本逻辑功能块可以配置成16×1,16×2或32×1的同步RAM,或16×1的双端口同步RAM,因此可以在FPGA内部配置高速双口RAM用来作为信号传输的数据缓冲器。同时,为了节省FPGA的内部逻辑资源,在FPGA外围配置了适当的SRAM用来存储数据。

3 视频积累算法在FPGA上的实现

通常视频积累的工程实现有多种方法。从时域上来说,视频积累是将连续N个重复周期同一距离单元的视频回波信号进行叠加,因此实现脉冲串积累离不开延迟线。在使用FPGA实现数字延迟线时,需要将前面N-1个周期的信号量化后存储起来,这样做需要较大的存储量和运算量。所以在实际工程中,常采用滑窗检测器用于天线波束扫过目标时收到回波脉冲数N较少的场合,但是若N值仍然较大,则滑窗检测器仍需要有很大的存储量。因此,在采用FPGA实现视频积累时,采用小滑窗检测器更适合于FPGA的特点。

评论