基于SoPC的低应变反射波检测系统

摘 要:提出了一种基于核心处理单元为Altera NiosⅡ的SoPC的智能低应变反射波检测系统。介绍了低应变反射波检测法,探讨了系统具体的软硬件设计。系统的主要目的是使复杂电子系统可在单块FPGA上实现,该系统在基桩完整性检测中具有广阔的应用前景,并能通过适当改进,应用于其他工程检测中。

本文引用地址:https://www.eepw.com.cn/article/191577.htm信息化、自动化、智能化、高集成度已经成为当今工程技术领域的发展趋势,并广泛应用于各个领域。可编程片上系统(SoPC)技术将中央处理器、内存、I/O接口以及大型可编程数字逻辑单元融合到单块FPGA芯片上,使得整个系统小型化、集成度高、灵活性强、功耗低且成本低廉。

基桩的低应变完整性测试因其简单易用及较低的成本,被广泛用于分析和*价基桩的工程建造质量。大多数传统的低应变桩身检测仪器都采用独立的单元:包括信号调制单元、模数转换器、存储器、微控制器及其外围电路和PC104工控机。因此,其很难在功耗、成本及抗噪性上令人满意。本文提出了一种基于以Altera NiosⅡ软核处理器为核心单元的SoPC的智能低应变反射波检测系统。该系统的硬件结构包括信号采集单元、存储器模块、电源模块、LCD触摸屏、USB/UART接口及SoPC模块Altera CycloneⅡ EP2C8。

1 低应变反射波法简介

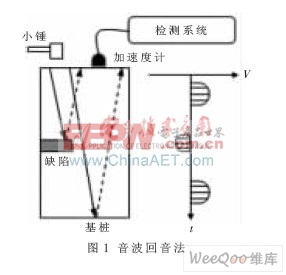

大多数的基桩缺陷检测都是基于音波回音法,低应变反射波法也不例外。在该方法中,通过直径4~5 cm的小锤敲击基桩顶部得到震源。再利用基桩上的加速度计来捕获记录加速度的变化情况,进而计算得到速度时间曲线。其示意图如图1所示。

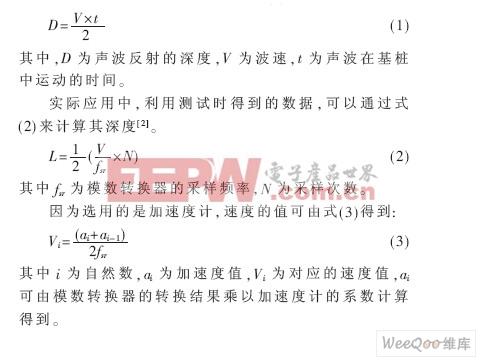

图1中横坐标为速度,纵坐标为时间。该测试记录能反映出震源波在桩内的运动情况。根据一维波理论,声波信号的幅度是一个与基桩阻抗相关的函数。因此,基桩的长度及缺陷的位置便可由式(1)计算得到。

2 系统组成与设计原理

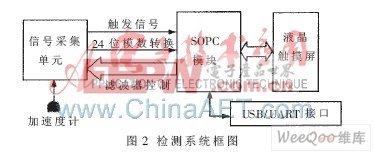

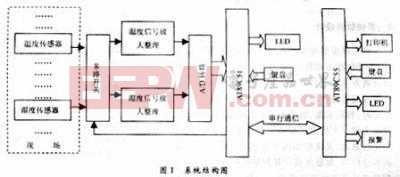

根据上述介绍,不难得知系统设计的关键便是获取低应变反射波的波速及模数转换器的采样频率。整个系统由加速度传感器、信号采集单元、SoPC模块、电源模块及其他外设电路组成,如图2。

将加速度传感器按照规范要求,安装在桩头磨好的位置,用黄油等介质进行耦合。用手持小锤进行敲击后,进入检测进程。首先由信号采集单元收集加速度传感器的输出信号,信号经过与加速度传感器输出端并联的电阻处理,由电流信号变为电压信号,并通过滤波器处理滤掉高频噪音后,经模数转换器捕获超过阈值电压的信号,并将转换后的信号存储到外部闪存中。最后由控制核心模块读取闪存中的数值并进行数据处理,将采集到的反射波形显示到系统的触摸显示屏上。并可通过USB/UART接口,将这些数据传输给PC机。

3 系统的硬件设计

3.1 SoPC模块设计

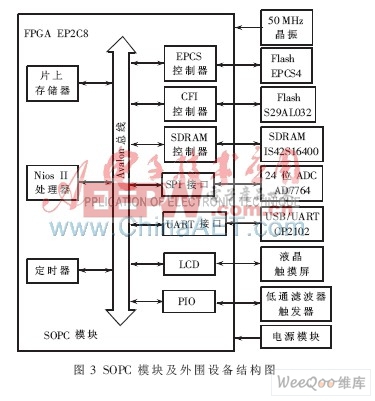

基于Cyclone Ⅱ FPGA EP2C8的SoPC模块是整个系统的核心。如图3所示,NiosⅡ软核处理器通过定义了主从设备之间接口与通信时序的Avalon交换式总线连接多个IP核。SoPC Builder也支持在设计中整合自定义的IP核。

根据系统结构需求,IP核的设计如下:

NiosⅡ/经济型软核处理器:SoPC Builder中包含三种可选的软核处理器。NiosⅡ/经济型软核处理器具备最小的体积,完全能满足本设计的应用需求。

片上存储器:EP2C8 FPGA提供165 888 bit的RAM内存,共计36个M4k的存储块。

定时器模块提供了系统所需的时钟中断。

并行输入输出模块(PIO)通过2 bit的二进制信号来控制滤波器的截止频率,并负责检测触发信号。

串行外设接口(SPI)作为从属设备来与模数转换器通信。

通用异步收发器(UART)提供了人机交互接口。反射波数据经过采集和调制后,可以通过USB-UART转换芯片CP2102将其由SoPC模块上传至电脑做进一步的处理。这里,USB接口可被视作一个虚拟的通用异步收发器来访问。

LCD模块用来控制分辨率为320×240的液晶触摸屏,其参数可自行定制。

EPCS、CFI和SDRAM控制器的作用是控制外围扩展存储器。EPCS控制器在系统启动时从EPCS4(串行配置芯片)下载硬件配置文件到FPGA。CFI(通用闪存接口)控制器具备32 Mb的Avalon接口(S29AL032),SDRAM控制器同样也具备64 Mb的Avalon接口,为访问存储器提供了便利。系统运行中,闪存存储配置文件,而SDRAM存储各类数据。

所有的模块将由用户或SoPC Builder指派不同的地址。NiosⅡ处理器通过Avalon总线访问这些模块或外部设备。

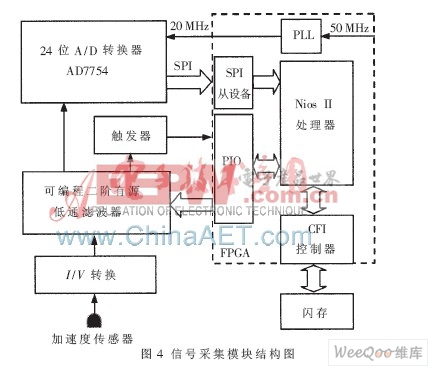

3.2 信号采集模块

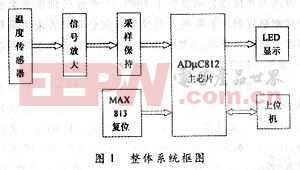

选择用于低应变反射波检测系统的加速度传感器,必须使其与小锤在敲击后产生的反射波的频率匹配。一般来说,用于基桩无损检测的有效信号频率为0~2 kHz,加速度传感器LC0104T正好满足这个条件,其敏感度为100 mV/g,量程为50 g,且频率范围达到9 kHz,安装谐振点为27 kHz。基于SoPC的信号采集模块信道噪声低,精度高,如图4。

加速度传感器的输出端与20 kΩ的电阻并联,将电流信号转换成毫伏级的电压信号。在信号传输过程中,用二阶有源巴特沃斯低通滤波器来优化信号,并过滤掉高频噪声。NiosⅡ通过PIO可以控制4个可编程中断的频率,分别是500 Hz、1 kHz、2 kHz和4 kHz。

AD7764是一种高性能、高速率、24位的Σ-Δ型A/D转换器,融合了宽输入带宽、高速率的特性,312 kHz输出数据速率时动态范围为109 dB,并且与FPGA有着灵活的SPI接口(SCO、nFSO、SDO、SDI)。FPGA中50 MHz的外部时钟信号可通过锁相环分频输出20 MHz时钟信号,以此驱动AD7764的MCLK,并使A/D转换器的nRESET端口在每个MCLK时钟周期中被置低,这样,NiosⅡ就可以通过SPI从模块读取包括24位转换数据的32位信号。

为了记录整个波形,低应变反射波的采样流程如下:通过LCD触摸屏发出采集信号指令,当触发器侦测到通过滤波器的输入信号的电压达到阈值电压时,便传送给NiosⅡ处理器一个低电平到高电平的跳变信号,NiosⅡ处理器马上记录此阈值电压信号的存储地址。A/D转换器开始捕获1 024个采样的输入信号,NiosⅡ将24位转换数据写入外部闪存S29AL032中。最终,通过对加速度传感器的数据处理,整个波形就可以用多个这样的存储地址中的数据,通过式(3)复原。

4 系统的软件设计

4.1 基于NiosⅡ IDE的软件开发

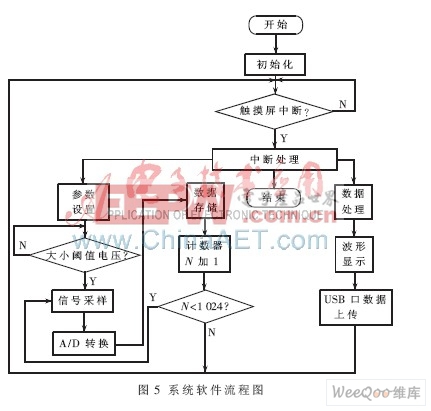

此开发环境可在进行软件设计时,自动根据NiosⅡ处理器系统的需求生成开发向导,包括:硬件抽象层、可调节的实时操作系统和设备驱动[5],避免了手动设置带来的不便,从而节省了时间,缩短了开发周期。基于SoPC平台NiosⅡ处理器的软件开发环境有了很大的发展,整个软件系统由分别实现不同软件功能的模块组成,模块包括:主程序模块、中断子程序、A/D转换子程序、数据处理子程序、LCD显示屏控制程序和触摸子程序。图5是整体软件设计的流程。

开始初始化后,对桩长等参数进行设置,然后通过触摸屏中断的方式选择相应的中断子程序。收到触发信号并开始检测后,信号采集模块将加速度传感器输出的信号与阈值电压进行比较,把有用的信号经A/D转换存储到寄存器中。在采集信号存储完后,通过触摸屏选择数据处理中断子程序功能,开始对寄存器中的数据按第1部分中提到的算法进行处理,并将波形结果显示在触摸显示屏上。并可由触摸屏选择USB接口中断子程序,将所有数据上传给PC机,做进一步的分析和计算。

4.2 μClinux操作系统的移植

将μClinux移植到SoPC模块中,可以使系统表现出完好的实时性和稳定性。μClinux操作系统可以和没有内存管理单元(mmu)的NiosⅡ处理器兼容,并且可以下载到嵌入式硬件平台中。

首先,在Linux Developer Bash开发环境中配置和构建内核。建立映像文件和linux.flash,生成的linux.flash文件即为μClinux的内核映像。将linux.flash文件下载到SoPC模块中,完成内核映像的加载。

除了装载内核,还要装载根文件系统。μClinux使用romfs文件系统,比一般的ext2文件系统需求空间更小。在宿主机Linux的target目录为μClinux下的根目录,用当前的脚本和工具将其转换成映像文件romdisk.flash。然后根据 userland/.config文件中相应变量的指示将应用程序二进制拷贝到target目录中,将应用程序加载到文件系统中并更新romdisk.flash文件,最后下载romdisk.flash文件到SoPC模块中。这样,就可以将μClinux操作系统及应用程序成功地移植到SoPC模块。

本系统充分利用SoPC的高集成性和灵活性,将复杂的电子系统简单化、小型化,不仅节约了开发成本也更适应绿色电子产品低功耗、耗材少的要求。

经实际测试,用本系统检测一根桩长为5 m的基桩,数据采集和处理正常,能通过预设的软件将结果显示在触摸屏上(如图6所示)。并能成功地与PC机进行传输,将采集的波形送至PC机进行进一步的分析。测试表明系统具有方便易用、可裁剪性强、扩展方便等特点,具有广泛的市场前景。

评论