基于CPLD/FPGA的多串口设计与实现

摘要:在工业控制中如何提高一对多的串口通讯可靠性和系统的集成性成为研究热点。本文利用嵌入式技术,提出基于CPLD/FPGA的多串口扩展设计方案。实现并行口到多个全双工异步通讯口之间的转换,并根据嵌入式系统实时性的需要,在每个UART接收器中开辟了8个接收缓冲单元,实现高速嵌入式CPU与RS232通讯设备之间的速度匹配,同时,串行口波特率等参数可根据需要进行设置。通过实践证明,本文设计的基于CPLD/FPGA的多串口完全符合工业控制中一对多串口通讯的要求。

关键词:CPLD/FPGA;多串口扩展;全双工;异步通信;嵌入式系统

在工业控制中,设备的通讯与控制主要采用简洁高效的串口方式进行。工控机通过PCI扩展卡方式进行串口的扩展,或采用电路复杂的扩展芯片实现串口扩展。随着嵌入式技术发展,嵌入式系统的应用逐步代替了成本高昂的工业控制计算机。为了简化硬件电路的设计,降低系统成本,本文提出了一种基于CPLD/FPGA多串口扩展的方案,实现多个外设串口的扩展和管理,同时解决一对多的串口通讯可靠性问题,满足嵌入式系统串口扩展的需求。

1 系统结构

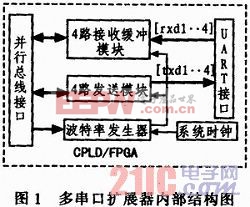

本设计以CPLD/FPGA芯片为核心,在芯片内部通过设计、编程实现并行总线接口到多个串行口的扩展。设计的多串口扩展包括并行总线接口、4路接收缓冲器、4路发送器、波特率发生器和UART接口。为实现高速嵌入式CPU与RS232通讯设备之间的速度匹配,充分利用嵌入式系统的实时性,在每个接收缓冲器中开辟了8个接收缓冲单元。在实际应用中,可根据嵌入式系统扩展的需要,灵活增减串口数量以及接收缓冲单元个数。在通讯过程,波特率发生器的时钟信号由外部有源晶振提供,选择合适的晶振频率即可获得高性能的数据传输。系统结构如图1所示。

2 功能模块设计

2.1 接收缓冲模块

2.1.1 接收缓冲模块构架

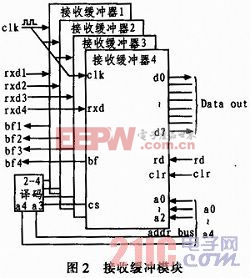

在设计过程中,为便于串口扩展功能的实现,将功能相似的部件进行了集成。本设计以4路UART接口扩展为例,接收缓冲部分包含了4个独立的接收缓冲器,其结构如图2所示。接收缓冲器共用clk时钟信号,并将其作为串行数据接收的波特率;每个接收缓冲器均有单独的rxd、bf、cs引脚,其功能分别为:串行数据输入、接收缓冲器储存状态、接收缓冲器片选。各接收缓冲器的片选端分别与2-4译码器的输出脚相连。译码器的输入端构成了4路接收缓冲器选择的地址线,分别对应a3、a4脚;结构图中数据总线d0~d7、读缓冲端rd、缓冲储存状态清‘0’端clr和缓冲单元地址线a0~a2为共用信号端口,分别与4个接收缓冲器相连。

评论