基于CPLD/FPGA的多串口设计与实现

2)写控制器

写控制器的ad_cnt端接收到RXD接收器的reg_flag负脉冲信号后,对地址寄存器进行加‘1’操作,并将新的地址状态送至双端口RAM的地址总线a0~a2。同时,reg_flag负脉冲触发写控制器对clk时钟计数,向双端口RAM产生cs片选信号和wr写控制信号,将RXD接收器d0~d7的数据写入双端口RAM地址线所对应的存储单元中。

3)双端口RAM

通过一系列时序信号的组合,RXD接收器接收的数据将暂存到双端口RAM中。本设计中,双端口RAM直接调用的Quartus8.0存储器子库中的LPM_RAM_DP元件。

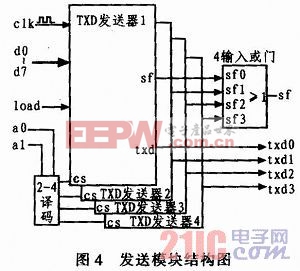

2.2 发送模块

发送部分由4路并行的TXD发送器、2-4译码器和4输入或门组成,如图4所示。4路TXD发送器共用时钟信号clk、数据端d0~d7、发送启动端load;每个发送器均有单独sf、cs、txd引脚,其功能分别为:发送状态标志、TXD发送器选择、串行数据输出。TXD发送器的cs端分别与2-4译码器的输出脚相连,译码器的输入端a0~a1即构成发送部分的地址线;发送器的sf端经过4输入或门输出,构成发送部分的发送状态标志。本文引用地址:http://www.eepw.com.cn/article/191085.htm

在通讯过程中,load脚接收到CPU的控制信号后,根据地址线a0~a1的组合选择相应的TXD发送器,将数据总线d0~d7上的数据通过txd脚逐位输出,通过串行总线发送至接收设备。一个字节发送完成后,发送状态端sf置‘0’,CPU可检测sf端的电平状态,以判断数据是否发送完成,也可以利用sf引脚的状态触发CPU中断,完成多个数据的连续发送。发送器的程序与接收器相匹配,在此不再阐述。

2.3 波特率发生器

UART的接收和发送按照相同的波特率进行数据传送。波特率发生器分别给接收部分和发送部分提供时钟信号,并且接收的波特率时钟是发送的16倍,利用16倍波特率时钟对串行数据进行高速采样,以确保接收数据的准确性。为实现与不同传输速率的串行设备通信,波特率发生器对系统时钟进行不同系数的分频,根据CPU控制线的组合可分别产生4800bit/s、9600bit/s、19200bit/s、38400bit/s等多种波特率。

3 仿真与实现

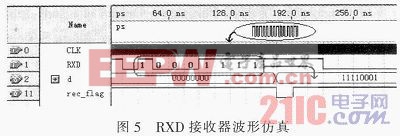

本串口扩展器通过VHDL编程,在Ouartus8.0下进行了仿真。由于仿真信号较多,仅对关键部件的信号进行分析。图5给出了RXD接收器仿真波形。在测试过程中,首先确定通信的波特率为19 200 bit/s,即RXD接收器CLK时钟为波特率的16倍,发送设备通过串行总线向RXD接收器发送F1H,当RXD接收器完成数据的接收后,立即将数据送至数据总线d0~d7,仿真结果如图5所示。

给写控制器的ad_cnt端输入地址计数脉冲,地址线a0~a2进行加‘1’操作,片选线cs和写操作端wr根据CLK时钟信号相应输出低电平,完成接收数据的写存储。连续存储8个字节后,缓冲器状态标志bf置‘1’。将clr端输入低电平,bf标志清‘0’,同时地址线a0~a2回到“000”状态。写控制器的仿真结果如图6所示。

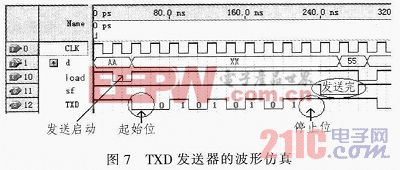

给TXD发送器的数据总线d0~d7输入AAH,通过串行总线发送至接收设备。load端置‘0’,启动发送。发送完成后,sf标志清‘0’。检查接收设备的接收值,与发送数据完全匹配。TXD发送器的波形仿真结果如图7所示。

4 结束语

本文详细介绍了CPLD/FPGA多串口设计的内部构成,对各个模块的工作原理和关键信号进行了分析,给出了EDA软件仿真形波和测试结果。通过对FPGA/CPLD多串口的设计与实现,为嵌入式系统中串口的扩展提供了一定的帮助。

评论