基于软件测试技术的FPGA测试研究

现场可编程门阵列(FPGA)的出现大大压缩了电子产品研发的周期和成本,由于FPGA器件具有高密度、低功耗、高速、高可靠性等优点,在航空、航天、通信、工业控制等方面得到了大量应用。随着FPGA应用领域的扩展以及重要性和复杂程度的提高,其可靠性问题变得越来越突出,因此对FPGA系统的测试需求变得尤为迫切。

目前FPGA测试技术的研究主要集中于对FPGA芯片资源的测试,通过编程覆盖FPGA所有的逻辑资源[1,2]和连接资源[3],验证每个单元基本逻辑功能的正确性,而无法对电路的整体行为进行有效的验证。硬件描述语言(HDL)是FPGA电路设计的主要实现方式,和软件一样,HDL也是人脑思维的逻辑产物,同样存在着不希望或不可接受的人为错误。随着设计复杂程度的提高,由HDL引入的缺陷成为影响FPGA可靠运行的关键因素,对FPGA电路行为的测试成为提高系统质量和可靠性的重要环节。

MIN Y.H.提出了在FPGA系统中进行高层测试的必要性[4]。高层测试即任何高于门级的测试,考虑的是高层描述,如HDL、状态图、功能块图等,通过高层测试发现设计中的缺陷,并在系统的开发阶段充分考虑测试需求,指导系统设计。以此为基础,先后提出了一系列具体的实施方法,如层次化的测试方法、基于电路功能或结构的测试方法、基于模拟的测试方法等。

1 研究背景

1.1 软件测试技术概述

在IEEE的软件工程标准术语中,软件测试定义为使用人工和自动手段来运行或测试某个系统的过程,其目的在于检验它是否满足规定的需求或找出预期结果与实际结果之间的差别。

按照测试级别,软件测试包括单元测试、部件测试、配置项测试、系统测试等;按照测试方法,软件测试可分为动态测试和静态测试,动态测试又可分为黑盒测试和白盒测试。静态测试包括了代码审查、静态分析、代码走查等测试类型;动态测试包括逻辑测试、功能测试、性能测试、接口测试等测试类型。白盒测试通常采用以逻辑覆盖衡量的结构性测试技术;黑盒测试通常采用包括功能分解、等价类划分、边界值分析等在内的功能性测试技术[5]。

1.2 FPGA系统的特点

FPGA作为可编程逻辑器件,通过编程的方式(如HDL)将通用芯片配置成用户需要的硬件数字电路,FPGA和软件系统具有相似的结构和开发方式,HDL与软件都是人脑思维逻辑的产物,具有相似的语法和失效机理。因此,将软件测试的成熟技术用于FPGA测试,在理论和操作上均具有可行性。

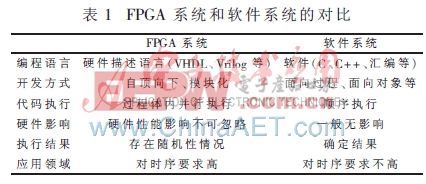

但是,由于软硬件系统本质上的不同,FPGA和软件系统在测试要求上存在一定的差异,表1从开发方式、代码执行顺序、受硬件影响程度、执行结果的随机性以及应用领域等方面,归纳了FPGA和软件系统的不同之处。

2 FPGA特有测试要求

针对FPGA和软件系统的差异,存在不同于软件测试特有的测试要求,包括HDL代码检测要求、测试级别要求和时序测试用例设计要求等。

2.1 HDL代码检测要求

由于HDL代码并行执行并存在硬件环境的影响以及竞争、冒险等不确定结果,在白盒测试中具有不同于软件测试的要求。一方面,不同于软件的控制流和数据流,并行程序的时序和信号流是一对相互依存的信息,程序的逻辑状态由二者共同确定。这就要求在测试中,既要依据信号流图对组合逻辑进行验证,还要依据时序图分析时变信号的时序一致性。另一方面,硬件特征对运行结果的影响也是代码检测中需要考虑的因素[6]。在编码规范的制定上,应当充分考虑并行程序的特点,正确处理与硬件资源之间的关系,避免竞争、冒险等不确定结果的产生。

2.2 测试级别的要求

与传统自底向上的电子设计技术不同,FPGA采用与软件开发相同的自顶向下的设计方法。一个项目的开发过程,从系统的分解、RTL模型的建立、门级模型的产生,到最终的可以物理布线实现的底层电路,是一个从高抽象级别到低抽象级别的开发周期。在开发过程中,需要在每一阶段分别进行行为仿真、功能仿真、门级时序仿真等仿真验证,而在测试阶段需要自底向上依次从门级、元件功能级到系统行为级进行测试。

2.3 时序测试用例设计要求

FPGA的并行运算和高响应速度的特性,使其在对高速时序逻辑的处理中得到广泛应用。因此对FPGA系统功能、性能的测试中,不能仅仅局限于对稳态输入输出的验证,还需要验证系统对时序信号的响应及输出量随时间变化正确性的判断。因此在测试用例的设计中,需要对系统输入、输出的时间变化趋势进行规定,并提供动态输出信号的判断准则,同时需要开发时序测试环境支持测试用例的执行。

3 FPGA测试技术框架

3.1 测试级别

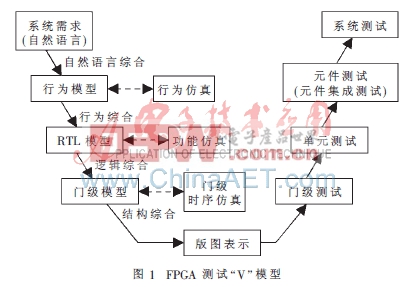

把抽象的实体结合成单个或统一实体的过程称为综合,FPGA系统的每一步开发过程都可以称为一个综合环节,即将自然语言表示经过自然语言综合转换为HDL算法表示,再通过行为综合转换在寄存器传输(RTL)级,进一步通过逻辑综合转换为逻辑门的表示,最终通过结构综合转换为版图表示。对于每一个综合环节,都对应响应的测试级别,FPGA测试的“V”模型如图1所示。

评论