基于CPLD的简易数字频率计的设计

摘要:CPLD器件的出现给现代电子设计带来了极大的方便和灵活性,使复杂的数字电子系统设计变为芯片级设计,同时还可以很方便地对设计进行在线修改。首先介绍了频率计的测频原理,然后利用CPLD芯片进行测频计数,从而实现了简易数字频率计的设计。此频率计的设计采用基于VHDL的“Top-Down”(自上而下)的设计方法,从系统总体要求出发,自上而下地逐步将设计内容细化,最后完成系统硬件的整体设计。所设计的电路在GW48系列SoPC/EDA实验箱上通过硬件仿真,下载到目标器件上运行,能够满足实际测量频率的要求。

关键词:CPLD;VHDL;频率计;设计

0 引言

目前已经有不少文献分别从不同的角度对此问题进行了讨论和研究。有基于FPGA实现的,FPGA的保密性差,它的分段式布线结构决定了其延迟的不可预测性,它的编程信息需存放在外部存储器上,使用方法复杂;也有用标准逻辑器件实现的,用标准逻辑器件使系统布线复杂、体积功耗大、可靠性差、设计周期长,交流和修改不方便。该频率计采用先进的EDA技术及自上而下的设计,使用CPLD芯片,CPLD具有连续连接结构,易于预测延时,使电路仿真更加准确,且编程方便、速度快、集成度高、价格低,从而使系统研制周期大大缩短,产品的性能价格比提高。本频率计采用流行的VHDL语言编程,并在设计平台实现了全部编程设计。该数字频率计的设计及实现具有良好的应用价值和推

广前景。下面对该频率计的软硬件设计进行详细论述。

1 测频原理

1.1 频率的定义

频率定义为在单位时间内,记录被测信号的变化周期数(或脉冲个数)。若记录被测信号的的变化周期数(或脉冲个数)为Nx,则被测频率Fx的数值为Nx,单位为:Hz。

1.2 基本性能指标

测频范围为:1 Hz~1 MHz;

测频精度:相对误差为1 Hz。

1.3 频率计的功能分析

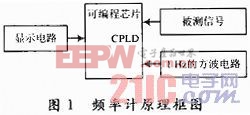

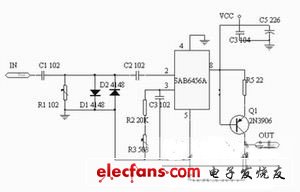

由于数字频率计是一个需对数字信号进行测量和显示的系统,由一片CPLD完成各种测试功能(对被测信号进行计数等),最后将测量结果送数码管显示输出,因此测频需要设置控制电路、计数电路、锁存电路、译码电路,将这些电路设计好的各部分连接起来成为一个整体的电路写人CPLD芯片中,外围电路由显示电路、产生1 Hz的方波电路组成。

控制电路是对计数电路、锁存电路和译码电路进行时序的控制。其控制要求为:先使计数电路在1 s内进行计数,接着在下一个1 s内锁存计数的结果,最后将锁存的数据进行译码和显示。在第一个测量显示周期结束后,控制电路将再次发出控制信号,先对功能电路清零,然后使系统开始第二个测量周期的工作。

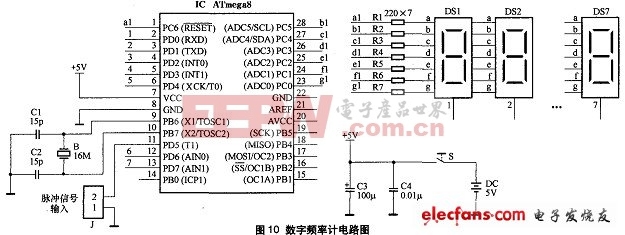

计数电路是对被测信号的频率进行计数的主功能电路。根据频率的定义和测频的基本原理,必须由一个脉宽为1 s的对被测信号脉冲计数的允许信号,其测量结果为被测信号在1 s内的脉冲个数,即被测信号的频率。由于被测信号的频率测频范围为1 Hz~1 MHz,因此用计数电路测量时,使用6个输出为4位的二进制数计数器。此计数器从个位开始到高位分别进行计数,使低位计数器的进位与高位计数器的被测信号输入端相连,从计数器电路的结构可知,该电路输出信号是由从低位到高位的多组4位二进制表示的十进制数组成的,用来分别表示被测信号的个、十、百、千等位的数值。

锁存电路的主要功能是对计数器计数输出的数据进行锁定保存。即使在前级计数电路的计数器清零以后,锁存器依然有保存的数据存在,不会造成数据的丢失。锁存电路中的锁存器是对单个十进制计数器数据进行保存,因此锁存器的个数与前一级计数电路的十进制计数器的个数相同。

译码电路的功能是将锁存器保存并将输出的4位二进制代码表示的十进制数进行译码转换,将其转换为能直接驱动数码管显示的十进制数字字符的输出信号。

显示电路由共阴数码管电路构成。由于被测信号的频率测频范围为1 Hz~1 MHz,因此需要6个数码管对其进行显示。

2 频率计各模块设计

2.1 频率计原理框图

此频率计的流程为:被测信号fin输入到CPLD芯片,在控制信号为1 Hz时,在CPLD芯片里完成对被测信号的测频、计数、锁存、译码,输出信号接数码管显示,如图1所示。

评论