CPLD与16C554在航空发动机参数采集器中的应用

0 引 言

随着航空工业和计算机工业的飞速发展,传统的机械式仪表已经逐渐被数字显示仪表所替代,嵌入式系统越来越多地应用于航空仪表之中。航空发动机是飞机上最重要的部件之一,需要测量的数据较多,而其各项参数对于驾驶员来说都是非常重要的信息,并且对信号采集的精度和实时性要求非常高。

发动机参数采集显示系统是航空电子系统的重要组成部分,也是座舱显示系统的一部分,它在飞行过程中显示发动机的状态给飞行员,使飞行员能够实时了解到发动机的工作情况。发动机参数采集显示系统由发动机参数采集器和发动机参数显示器2部分组成。发动机参数采集器的主要功能是对发动机主要传感器输出的信号进行调理、采集和处理并输出给显示设备进行显示。随着航空发动机及其附属系统越来越复杂,需要测量的参数以及需要进行数据交联的设备越来越多。这就要求发动机参数采集器具有实时性、可靠性、嵌入性等特点。同时还要考虑到低成本的设计原则和实际工程应用中低功耗的特点。这些条件在系统设计时都需要综合考虑以达到最优化的性能设计。

随着集成电路技术的高速发展,可编程专业集成电路的集成度越来越高,功能越来越强大,用可编程逻辑器件进行的集成设计已经逐步取代了基于标准逻辑器件的设计,成为专用集成电路(ASIC)设计的一个重要分支。更重要的是,利用新的Top-Down设计方法,使得系统的设计从一开始就能够在系统级的行为描述上得到验证,有效避免了系统设计上的错误,减少了设计过程的反复。因此,在嵌入式系统设计中使用可编程逻辑器件,是实现产品小型化、集成化、高可靠性、低成本和低功耗等的有效途径。

1 航空发动机参数采集器系统概述

航空发动机参数采集器的主要任务是采集发动机以及滑油系统、燃油系统、旋翼和主减速器的各项参数,进行数据处理和数据打包后,通过串行通讯链路发送给显示系统以及其他设备进行显示或使用;并且当出现告警时,将告警信号发送给告警系统;此外还输出传感器激励电源为传感器供电。需要采集的参数较多,主要类型有:模拟量、开关量以及频率量。根据发动机参数采集器系统的信号处理及数据通讯任务的特点,我们采用了美国德州仪器公司(以下简称美国TI公司)的TMS320C31浮点型数字信号处理器作为发动机参数采集器的控制核心。TMS320C31是TI公司的浮点型数字信号处理器,它是一种高性能32位微处理器,其内部总线采用了哈佛结构,即程序和数据采用2个独立的存储器,每个存储器独立编址和取址,故取址和编址能完全重叠运行;并采用流水线作业方式,1个时钟周期可执行1条指令;片内具有专用硬件乘法器,片上集成有40位浮点运算和其它功能,具有支持边界扫描测试功能等。TMS320C31处理器的中断资源包括4种外部中断:串口发送、接收中断,2个定时器中断及DMA中断,这些均为电平触发中断并且都可通过软件设置来完成。此外,TMS320C311个仿真器接口、2个互锁信号:XF0、XF1以及其它的保持、复位等信号。TMS320C31上述功能和特点,使得复杂的控制和算法完全可以在规定时间内完成,而且满足精度要求。

2.1 复杂可编程逻辑器件(CPLD)

可编程逻辑器件通常可分为3大类:通用阵列逻辑(generic array logic)、现场可编程门阵列(fieldprogrammable gate array)和复杂可编程逻辑器件(complex programmable logic device)。CPLD主要是由可编程逻辑宏单元围绕中心的可编程互连矩阵单元组成。发动机参数采集器系统选用了Xilinx公司的CPLD(XC95144)。按照逻辑关系,编写出逻辑控制方程,XC95144的程序通过JTAG接口的在线动态可编程专用电缆下载后,即可实现逻辑控制。

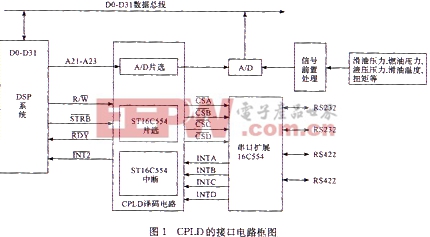

2.2 CPLD的接口电路

利用复杂可编程器件CPLD设计DSP扩展外设电路的译码电路,可以使设计者在系统内进行编程,布局、布线都很方便。芯片不必脱离线路板就可以更新设计并下载逻辑电路程序,真正实现了硬件软件化,从而使开发周期大大缩短,使设计风险大大缩小,CPLD的接口电路框图如图1所示。

本文最终实现的发动机参数采集器系统是在原有DSP组成的高速信号处理的基础上,外加了CPLD芯片构成。接口器件A/D、16C554和DSP的连接完全是通过CPLD实现的。由于使用了CPLD,在PCB设计阶段可根据需要调整引脚位置,走线距离缩短,使线路的抗电磁干扰能力增强,有效地减少了PCB设计的工作难度和系统的开发周期。

数据线、地址线等时序信号按照规定的逻辑关系工作。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间的可测性。本文设计所选用的CPLD是Xilinx公司的XC95144芯片,它有144个宏单元,3200个可用逻辑门,100个输入输出引脚(81个可用I/O引脚)。这一基于EEPROM的器件能够提供组合和传输延迟在15 ns以内,它的输入寄存器建立时间非常短,而且能够提供多个系统时钟,具有可编程的速度/功率控制。通过对系统所需的逻辑控制信号数目的分析,调试硬件时更改逻辑控制信号。按照逻辑关系,编写出逻辑控制方程,通过JTAG接口的在线动态可编程用专用电缆下载后,即可实现逻辑控制。

2.3 16C554在串口扩展中的应用

本文所设计的发动机参数采集器系统需要多个串行口与外界进行数据通信,而TI公司的TMS320C31数字信号处理器设计串口的方法一般是利用通用的I/O口线来构成串口,并由软件来设定波特率。这在DSP使用率较低的情况下比较有用;但是当通信实时性要求较高时,就应该通过扩展异步通信芯片来实现高速串行通信。

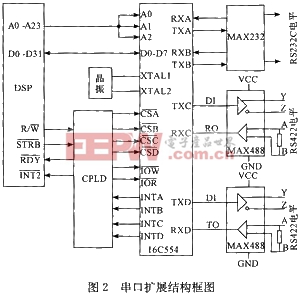

对于并口的设计方法,因为DSP输入/输出资源有限,因此,只能利用扩展异步通信芯片或者总线接口来扩展打印口。EXAR公司的异步通信芯片ST16C554正是可以同时实现扩展串行口和并行口通信的理想芯片。该芯片内含4个16C550异步通信单元,每个单元独立控制发送与接收,且具有16字节FIFO以减少中断请求次数,波特率发生器可编程。可以利用单一的中断源来管理多个扩展串口,并保证多个串口中断的无漏检测与应答。16C554与DSP的连接如图2所示。16C554内部共有12个寄存器,可分别用于对通信参数的设置、对线路状态的访问、数据的发送和接收以及中断管理等功能。通过外加电平转换芯片就可以实现RS232,RS422,RS485通信(本文所设计的发参系统没有采用RS485通信)。

2.4 串行口中断处理说明

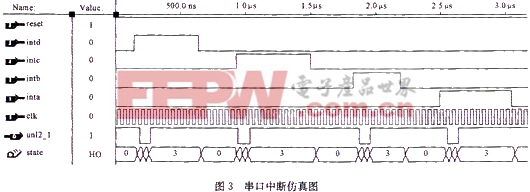

DSP TMS320C31不支持边沿触发中断方式只支持电平触发中断方式,而串行口ST16C554为边沿触发中断方式,因此需用CPLD将上边沿转化为一个脉宽合适的低电平窄脉冲。由于TMS320C31正H1时钟的下降沿检测中断引脚,因此,低电平窄脉冲的脉宽必须大于一个H1。另一方面,TMS320C31每两个H1时钟周期在同一个中断引脚检测一次中断,因此为了使DSP能识别外中断而且不被重复检测以免再次进入中断使系统混乱,必须使低电平窄脉冲的脉宽τ满足:1T≤τ≤2 T(T为H1/H3的周期)。

因为DSP外部中断引脚为4个,可用外部中断只有3个,而4路串口可以产生4个中断源,因此需通过CPLD处理,最后产生1路中断送至DSP,处理原理为当4路中任何一路有中断请求时就产生中断信号,并将4路中断的状态存入寄存器,DSP可利用数据线访问寄存器以确定具体是哪路产生的中断。

串行口中断处理仿真图如图3所示,功能是把串行口中断高电平转换为2个H3宽度的低脉冲。

3 软件设计

本文使用的CPLD开发系统是Xilinx公司的ISE 6.x系列,该开发工具功能强大,使用方便。使用美国国防部开发的超高速集成电路硬件描述语言(VHDL)、Verilog公司开发的Verilog HDL和电路图(schematic)中的任意一种设计方法均可。

3.1 CPLD的逻辑实现

系统通过地址线来对外部接口器件进行寻址,16C554的片选信号是通过CPLD来实现的,下面给出了VerilogHDL描述语言的程序:

3.2 异步串口通信程序的设计

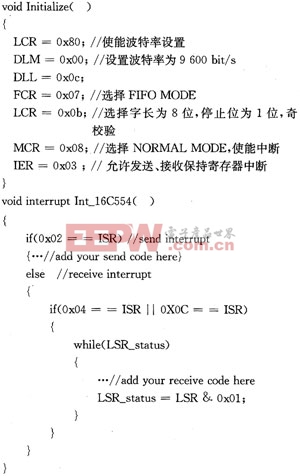

在本系统中,外部晶振频率为1.843 2MHz,通信格式为8位数据位,1位停止位,奇校验,工作在中断方式,16C554四个串口通道各自独立工作。串口初始化程序以及接收、发送中断读取程序如下:

4 结束语

通过16C554扩展串口,其硬件接口电路简单;复杂可编程器件CPLD的使用,将DSP较强的逻辑控制、数据处理能力以高集成度、高可靠性、高速度有机地结合起来,从而使设计的系统具有较高的性能价格比,设计成本和风险大大降低。

评论