ALF简介及IC设计流程

先进库格式(ALF)是一种提供了库元件、技术规则和互连模型的建模语言,不同抽象等级的ALF模型能被EDA同时用于IC规划、原型制作、实现、分析、优化和验证等应用中。本文在介绍ALF概念的基础上,详细讨论了使用ALF时库元件与IC的设计流程,同时还介绍了IC分层实现与原型制作的方法。

本文引用地址:https://www.eepw.com.cn/article/190690.htm在IC设计中,常常会发现半导体性能与得到的设计结果之间存在差距,这些差距最终要靠新一代EDA工具来弥合。一般说来,要想消除差距就必须将以前孤立的设计任务集成到一起,或者将以前零散的设计方案进行统一。

例如过去在设计和测试之间就存在隔阂,现在用可测性设计的概念可加以解决,在综合和布局之间的矛盾最近也有了物理综合概念方案,下一个计划目标是针对设计和掩膜生成之间的问题,希望能用可制造性设计的概念解决。

然而在库的创建和具体设计之间依然还存在矛盾,就像数据总在前后端设计之间传来传去类似,带有预定义建模概念的库也是在供应商和用户之间倒来倒去。

库元件由供应商进行定义,建模概念则是EDA应用所要求的,设计人员没有选择,有什么库元件就只能用什么,不可能去深入理解更不用说修改了,库的内容可能会超出所选EDA工具处理的范围。随着设计复杂性、性能和费用不断增加,预定义库的概念也很成问题,例如在设计项目开始时,用户可能会在用于某种特定技术的库实际出现以前,就希望能了解用该技术实现设计是否有意义。

在设计实现过程中,用户需要创建一些模块作为可重复使用的库元件,结束时如果可用库元件(如具有正确驱动能力的单元)不多,用户将只需做很少的布局优化就能满足性能目标。在设计过程中任何时候,用户都可能要按不同程度的抽象和精度对时序、功率、电气性能、拥塞、路由性能及其它设计特性进行评估。

Accellera ALF是一个新完成的IEEE标准,其设计可使用户对库及设计流程中的应用有更强的控制和影响能力。ALF不像传统库格式那样仅仅是一个数据信息库,它是一种智能型自扩展建模语言,可对库元素的功能、电气和物理模型,包括技术规则、单元、构建模块和互连等提供语义支持。

ALF支持完整的RTL到功能、ASIC和SoC技术库电气性能与布局视图的GDSII描述,适合从单元到复杂的分层设计模块。ALF是一个经生产验证的标准,得到先进半导体供应商和用于0.13μm及更小工艺技术的下一代EDA工具的支持。

ALF的抽象范围可用于行为、RTL、门级和布局,它不是凭空开发的,而是现有库格式的超集,很容易从现有格式转换过来。ALF的结构原理非常简单很容易掌握,它主要关注内容而不是格式细节和各种限制。

从应用的观点看,语言元素可和建模域联系起来,它可以是功能域、电气域或物理域。但ALF描述功能主要来自与域无关的语言元素,如模板(用于重复使用库描述)和算术模型(用于数学描述量的计算)。

库元件创建和描述

ALF可用来指定一个库元素如单元所需的功能和描述,单元规格包括单元名称和终端(即引脚)与单元所执行功能的形式描述,形式描述可以在VHDL或Verilog等语言中生成硬件描述语言(HDL)仿真模型。

可生成多种HDL模型用于不同的目的,这里的不同根据用户对模型风格的爱好而不是由单元功能来决定。例如某个模型可以用一种粗略的方式处理未知逻辑状态,以便快速仿真,而另一个模型则可用非常具体的方式处理未知逻辑状态,这样仿真就要慢一些,但更精确。ALF模型可作为公共参考,用于所有这些HDL模型。

单元的物理布局以GDSII格式表示,SPICE格式的晶体管级网表可从物理层中提取,这样的晶体管网表中包括了寄生电气分量。或者设计人员也可用手工或EDA工具创建晶体管网表,将ALF描述的功能规范映射到晶体管网表中。这种网表的精度要低于从布局中提取,但对制作原型库还是有用的。

晶体管网表和各钟HDL模型都能和ALF描述的功能规范进行比较,更重要的是,晶体管网表还能用来描述单元的性能,以便通过运行SPICE仿真来测量时序、功率、噪声和其它电气特性。

SPICE仿真由描述工具进行控制,该工具从ALF表示的规范中推断出相关信息,只要这个信息与单元本身的功能相关,例如需要描述的时序曲线可在ALF中表示,也可从ALF中推出。描述工具的输出是库单元模型,带有特性数据,同时也在ALF中表示,另外也可用库编辑器将所有库单元模型组合成一个二进制文件,作为EDA应用工具的数据准备。

IC实现与性能分析

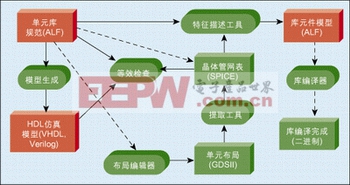

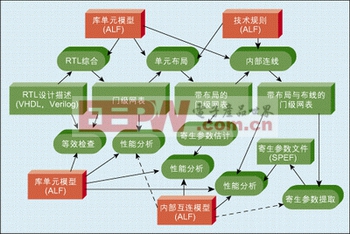

ALF库可用在以单元作为构建模块的IC实现流程中(图1)。在该流程里,RTL设计描述通过RTL综合工具转换成网表,网表含有单元示例,这里称为门而不是晶体管,它使用ALF库寻找将RTL描述映射到含有单元示例网表所需的库元件。ALF单元模型不会描述单元中的晶体管。

等价检查工具将RTL设计描述与网表进行比较,以确定RTL到网表的转换是否正确,它可用与RTL综合工具相同的ALF库。同样,HDL模拟工具(图1中没有显示)也能用来确定RTL设计描述和网表行为在响应给定激励时是否与预期的一样,该模拟工具可使用ALF模型或从ALF模型提取出来的HDL模型。

图1的流程已经进行了简化,像数据通路结构创建、与可测性设计(DFT)有关的结构创建以及特殊扫描插入等特殊网表转换没有显示在图中,ALF单元模型含有与这些应用有关的信息。

评论