接地问题问答总结

问:我已看过你们的“产品说明”(data sheets)和“应用笔记”(appl ication notes),也参加过你们的技术讲座,但有关如何处理ADC中模拟地和数字地的引脚 我仍有点儿糊涂。产品说明书中通常要求把模拟地和数字地在器件上连接在一起,但我不 想把ADC接成系统的星形接地点。我应该怎么做?

本文引用地址:https://www.eepw.com.cn/article/190074.htm答:首先,对涉及到模拟地和数字地感到糊涂这件事,你不必感觉那么坏,许 多人都是这样的!许多迷惑首先来自ADC接地引脚的名称。模拟地和数字地的引脚名称表示内 部元件本身的作用,未必意味着外部也应该按照内部作用去做。让我们来解释一下。

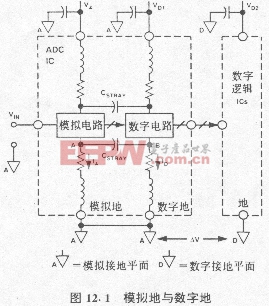

一个集成电路内部有模拟电路和数字电路两部分,例如ADC,为了避免数字信号耦合到模拟 电路中去,模拟地和数字地通常分开。图121所示是一个ADC的简单示意图。从芯片上的焊 点到封装引脚的连线所产生的引线接合电感和电阻,并不是IC设计者专门加上去的。快速变 化的数字电流在B点产生一个电压,经过杂散电容(C STRAY )必然耦合到模拟电路的A点 。尽 管这是制造芯片 过程中IC设计者应考虑的问题。可是你能够看到为了防止进一步耦合,模拟地和数字地的引 脚在外面应该用最短的连线接到同一个低阻抗的接地平面上。任何在数字地引脚附加的外部 阻抗都将在B点上引起较大的数字噪声。然后将大的数字噪声通过杂散电容耦合到模拟 电路上。可通过一个极简单的示意图(图121)来说明这一点。

问:好,你已告诉我把集成电路的模拟地和数字地引脚接到同一接地平面,但我 仍然要把模拟和数字接地平面在系统中分离开来,我要它们仅仅在一点上连起来,但这 个公共点是电源的返回端,并且连到底座接地线上。那么现在我还要做什么?

答:假如你的系统只有一个数据转换器,实际上你可以按照产品说明中所说的方 法去做 ,并且把模拟地和数字地线系统一起连在转换器上。你的系统的星形接地点现在是在数据转 换器上。但是这也许是极不希望的,除非在开始时你就用这样的想法来设计你的系统。假如 你有几个数据转换器安排在不同的印制线路板上,这个规则不适用应该另想办法,因为模 拟地 和数字地系统被连接在许多印制线路板的每个转换器上。对于接地环路这是最好的建议。

问:我已经能想像出来了!假如我必须把模拟地和数字地引脚在器件上连 在一 起,我仍旧需要分开系统的模拟地和数字地,我把模拟地和数字地连起来再接到印制线路板 上的模拟接地平面,或者是数字接地平面上,但不能两者都连上,对吗?因为ADC既是模 拟器件又是数字器件,那么连到哪一个接地平面更合适呢?

答:对!假如你把模拟地和数字地引脚都连到数字接地平面上,那么你的模拟输 入信号将有数字噪声叠加上去,因为模拟输入信号是单端的且相对于模拟接地平面而言。

问:所以正确的回答是把模拟地和数字地引脚两者连起来并接到模拟接地 平面上,对吗?但这样会不会把数字噪声加到本来很好的接地平面上?另外,因为现在输出信 号是相对于模拟接地平面,而所有其它逻辑是相对于数字接地平面,那么输出逻辑噪声容限 是否会下降?我打算把ADC输出接到印制线路板背面三态数据总线上,在那里噪声会相当大, 所以我认为首先需要能够得到的所有噪声容限。

答:好!没有什么人会说生活是很容易的!你已经通过困难的道路得到了正确的 结论,但你提出的模拟接地平面上的数字噪声和在ADC输出端上减少噪声容限(noise margin )的问题, 实际上并非像想象的那样坏,可以把它们克服掉。把几百毫伏不可靠的信号加到数字接口明 显地好 于把同样不可靠信号加到模拟输入端。对于10 V输入的16位ADC,其最低位信号仅仅 为150 μV!在数字地引脚上的数字地电流实际上不可能比这更坏,否则它们将使ADC内部 的 模拟部分首先失效!假如你在ADC电源引脚到模拟接地平面之间接一种高质量高频陶瓷电容器 (0 1μF)来旁路高频噪声,你将把这些电流隔离到集成电路周围非常小的范围,并且将其对 系统其余部分的影响减到最低。

虽然数字噪声容限会减少,但是如果低于几百毫伏,对于TTL和CMOS逻辑通常是可以接受 的。假如你的ADC有单端ECL输出,你就需 要在每一个数字门上加一个推挽门,即起平衡和补偿输出的作用。把这些门电路封装块地线 引 到模拟接地平面,并且用差分方式连接逻辑信号接口。在另一端使用一个差分线路接收器, 将 它的接地端接到数字接地平面上。模拟接地平面和数字接地平面之间的噪声是共模信号,它 们的大 多数将在差分线路接收器的输出端被衰减抑制掉。你可以把同样方法用于TTL和CMOS,但它 们通常有足够的噪声容限,所以不需要差分传输。

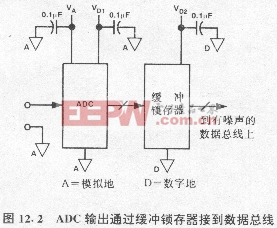

但是你说过的一件事使我大感忧虑。通常把ADC输出直接连到有噪声的数据总线上,是很 轻率的作法。总线噪声经过内部寄生电容耦合可能返回ADC模拟输入端。寄生电容从01到0 5 p F。如果把ADC输出直接连到靠近ADC的中间缓冲锁存器就要好得多(见图122)。缓冲锁存器 地线接到数字接地平面上,所以它的输出逻辑电平和系统其余部分的逻辑电平兼容。

评论