在便携式应用中,利用零功耗CPLD来降低系统总成本

可编程逻辑器件(PLD,Programmable Logic Device)的灵活性一直受到电子工程师的喜爱,但在各种移动式消费类电子产品市场仍然是ASIC芯片的天地。有几个原因阻碍着CPLD器件进入移动设备市场,尤其是各种基于电池供电的手持设备。一是其高昂的价格,二是其巨大的功耗,还有一个因素是CPLD器件的工作频率。同样规模的CPLD和ASIC,CPLD的最大工作频率往往低于专门设计的ASIC芯片。

本文引用地址:https://www.eepw.com.cn/article/190022.htm基于这种情况美国莱迪思半导体有限公司推出了ispMACH4000Z系列器件。该器件突破了CPLD器件进军移动式消费类电子产品市场所遇到的价格和速度门槛。IspMACH4000Z(In-System Programmable Macro Array CMOS Hight-densigy)系列器件的推出标志着莱迪思公司的第三代BFW(SuperBig,SuperFast,SuperWide)器件的面世。该系列器件的最高工作频率可达400MHz,完全能满足大部分当代消费类电子产品的高速应用场合。

通用CPLD应用

CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。其中MC结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

第一组应用介绍了CPLD所胜任的功能。虽然这些功能不是专门针对降低功耗的,但是,利用低功耗CPLD来实现这些功能对功耗有积极的影响。例如,一个常见的CPLD功能是合并分立逻辑。这可以节省PCB空间,降低材料(BOM)成本,并减小总体功耗。下面讨论一些常见的通用CPLD应用。

1. 上电排序

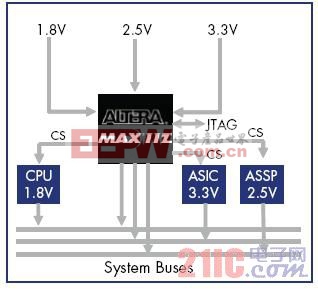

在许多产品中,各种器件的上电顺序非常重要,这使得上电排序成为一个关键的功能。CPLD在系统上电的几个毫秒内就开始工作,因此成为控制系统中各种器件(包括微处理器或微控制器)上电排序的最佳选择(图1)。上电排序仅仅是低功耗CPLD能够实现的多种系统功能的其中之一。可编程逻辑的最大价值在于可将多种功能在一个器件中实现。

图1:利用CPLD进行上电排序。

2. 电压转换

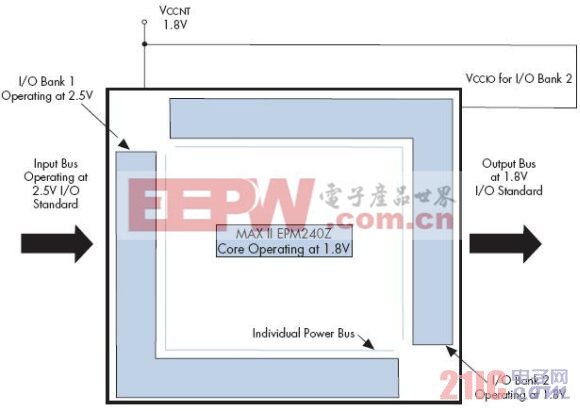

很多产品都需要使用电压不同的各种逻辑器件。为支持多电压应用,设计人员需要频繁连接不同电压的器件。CPLD拥有大量的I/O,它们被分组成多个块。每个I/O块被依次分配一个特有的电压电源。因此,开发电压转换器只需要将某一电压的所有I/O分组在一个块中,并将相关的电压基准连接到这些I/O所需的电源上(图2)。使用CPLD不但能够很好地完成电压转换,它更大的优势在于和电压转换相结合的可编程能力。例如,如果某一应用要求的LCD显示器不被主处理器所支持,且两者电压不同,那么可以利用CPLD来实现主处理器和LCD显示器之间的电压转换时序控制。

图2:利用Altera MAX IIZ CPLD进行电压转换。

评论