基于FPGA在弹上信息处理机中的应用

引言

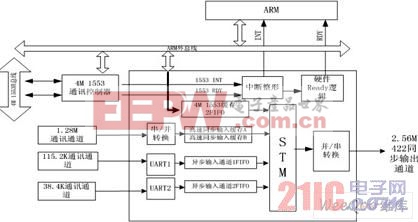

本文引用地址:https://www.eepw.com.cn/article/189986.htm信息处理机(图1)用于完成导弹上多路遥测信息的采集、处理、组包发送。主要功能包括高速1553B总线的数据收发 、422接口设备的数据加载与检测、多路数据融合和数据接收、处理、组包发送的功能。其中,总线数据和其他422接口送来的数据同时进行并行处理;各路输入信息按预定格式进行融合与输出;数据输出速率以高速同步422口的帧同步脉冲为源,如果高速同步422口异常不影响总线数据和其它422口的数据融合与输出功能。在CPU发生异常或总线数据异常时不影响其它422口数据的融合与输出功能;能够对从总线上接收的数据进行二次筛选、组包,并发送往总线,供其它设备接收。

图1 信息处理机功能框图弹上功能框图

系统设计

CPU选择

4M 1553B总线数据的采集,由4M总线智能通讯接口管理,经CPU接收、组包,再回到4M总线,发送至FPGA进行采集。CPU选择Atmel公司的AT91FR40162S, 内部自带256KB的SRAM和容量为2M x 8b FLASH存储器,主频最高可达75MHz。该ARM的等待电路由硬件等待逻辑产生,在FPGA内部实现。ARM外部中断源主要有:4M 1553B通讯控制器中断;20ms缓冲区切换中断。其中,4M 1553B通讯控制器中断信号经过FPGA整形后送入ARM。20ms缓冲区切换中断提供给FPGA内部各个同步、异步通讯IP组帧状态机用于缓冲区切换。

3路输入数字量接口

3路输入数字量,码速率分别为:1.28Mbps、115.2Kbps、38.4Kbps的数据流,数据流在FPGA内部经过串并转换将接收的数据存储在数据缓冲区A和数据缓冲区B中,再经过状态控制机来控制数据的不断更新。

评论