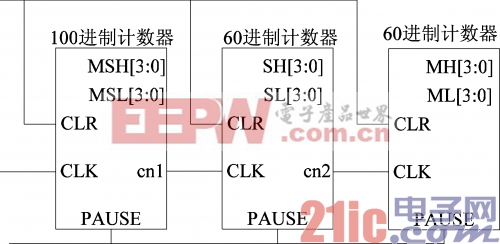

- CLK:时钟信号。

- CLR:异步复位信号。

- PAUSE:暂停信号。

- MSH、MSL:百分秒的高位和低位。

- SH、SL:秒信号的高位和低位。

- MH、ML:分钟信号的高位和低位。

下面是数字跑表的Verilog HDL源代码及说明。

module paobiao(CLK,CLR,PAUSE,MSH,MSL,SH,SL,MH,ML); //端口说明

input CLK,CLR;

input PAUSE;

output[3:0] MSH,MSL,SH,SL,MH,ML; //内部信号说明

reg[3:0] MSH,MSL,SH,SL,MH,ML;

reg cn1,cn2; //cn1为百分秒向秒的进位,cn2为秒向分的进位

//百分秒计数模块,每计满100,cn1 产生一个进位

always @(posedge CLK or posedge CLR) begin

if(CLR) begin //异步复位

{MSH,MSL}=8'h00;

cn1=0;

end

else if(!PAUSE) begin //PAUSE 为0时正常计数,为1时暂停计数

if(MSL==9) begin

MSL=0; //低位计数至10时,低位归零

if(MSH==9) begin

MSH=0; //低、高位计数至10时,高位归零

cn1=1; //低、高位计数至10时,触发进位位

end

else //低位计数至10,高位计数未至10时,高位计数

MSH=MSH+1;

end

else begin

MSL=MSL+1; //低位计数未至10时,低位计数

cn1=0; //低位计数未至10时,不触发进位位

end

end

end

//秒计数模块,每计满60,cn2 产生一个进位

always @(posedge cn1 or posedge CLR) begin

if(CLR) begin //异步复位

{SH,SL}=8'h00;

cn2=0;

end

else if(SL==9) begin

SL=0; //低位计数至10时,低位归零

if(SH==5) begin

SH=0; //低位计数至10,高位计数至6时,高位归零

cn2=1; //低位计数至10,高位计数至6时,触发进位位

end

else

SH=SH+1; //低位计数至10,高位计未数至6时,高位计数

end

else begin

SL=SL+1; //低位计数未至10时,低位计数

cn2=0; //低位计数未至10时,不触发进位位

end

end

//分钟计数模块,每计满60,系统自动清零

always @(posedge cn2 or posedge CLR) begin

if(CLR) begin //异步复位

{MH,ML}=8'h00;

end

else if(ML==9) begin

ML=0; //低位计数至10时,低位归零

if(MH==5)

MH=0; //低位计数至10,高位计数至6时,高位归零

else

MH=MH+1; //低位计数至10,高位计未数至6时,高位计数

end

else

ML=ML+1; //低位计数未至10时,低位计数

end

endmodule

通过上面的这3个模块,即可实现数字跑表的功能。

评论