串行A/D转换器MAX1270及其应用

1. 引言

本文引用地址:https://www.eepw.com.cn/article/188780.htm目前A/D转换器的种类繁多,从数据输出形式上可分为串行输出与并行输出两大类。其中串行输出AD转换器因其硬件接口简单而得到广泛应用。另外,从可接受的输入信号极性上看,A/D转换器又可分为单极性输入和双极性输入。在很多的数据采集场合常常面对极性可变的模拟信号。当然可将待转换信号进行电位移动以将其转化为单一极性,但如此便增加了电路的复杂性。串行输出、双极性输入A/D转换器MAX1270[1]不增加任何硬件电路即可实现对双极性模拟信号的A/D转换。迄今为止对MAX1270的应用非常少[2],且未见详细介绍。本文详细介绍了MAX1270的特点,给出了最简硬件接口、软件编程及应用实例。

2. MAX1270芯片介绍

MAX1270是8通道、多量程双极性输入、串行输出、逐次逼近型12 bit AD转换器。其封装形式有24脚Narrow PDIP和28脚SSOP两种。PDIP封装的引脚排列如图1所示。各有用引脚功能如下:

1-VDD,+5V电源输入端;2、4-DGND,数字地;5-SCLK,串行时钟输入端;6-/CS,片选输入端,低电平有效;7-DIN,串行数据输入,即AD转换控制字输入端;8-SSTRB,串行数据输出选通输出端;10-DOUT,串行数据输出端;11-/SHDN,掉电模式控制输入端,

低电平有效;12-AGND,模拟地;13~20-CH0~CH7,模拟信号输入端;21-REFADJ,参考电压输出/外部调节输入;23-REF,参考电压缓冲输出/ADC的参考输入。

2.1 MAX1270的控制字

MAX1270的8位控制字及其功能如表1所示。最高位START为起始位(高电平),标志控制字的开始。/CS为低电平期间,控制字在时钟脉冲SCLK作用下先高位后低位通过DIN端输入。

表1 控制字格式

BIT7(MSB) | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0(LSB) |

START | SEL2 | SEL1 | SEL0 | RNG | BIP | PD1 | PD0 |

2.2时钟模式与转换速率

PD1PD0为掉电/时钟模式选择位。PD1PD0=10、11时为省电模式。正常工作时MAX1270有外部时钟与内部时钟两种工作模式。PD1PD0=01时为外部时钟模式,串行数据的移入、移出以及数据采集、转换都由SLCK端的输入脉冲控制。PD1PD0=00时为内部时钟模式,数据转换时钟由芯片自己产生,减轻了微处理器的负担,使得转换后的数据可在微处理器方便的任何时刻读取,利于提高微处理器的工作效率。外部时钟模式分为25SCLK/s(每个数据转换需要25个时钟周期)和18 SCLK/s两种方式,后者转换速率稍快的原因是在全部数据转换期间/CS始终维持有效电平。内部时钟模式也有20、16、13 SCLK/s等不同转换方式。不同的时钟模式和转换方式,其转换速率不同。在外部时钟模式、SCLK速率为2MHz、18 SCLK/s时MAX1270转换速率可达110ksps。

2.3通道选择与输入范围

SEL2~SEL0为通道选择位,000~111分别选择输入通道CH0~CH7。RNG~BIP为输入范围选择位,MAX1270有4种输入范围。RNG~BIP置00时 0~5V单极性输入, 置01时0~+10V单极性输入; 置10时 -5~+5V双极性输入;置11时-10~+10V双极性输入。

2.4传输函数与输出数据格式

对单极性输入,1LSB=FS/4096,输出数据为12位二进制码。对双极性输入,1LSB=FS/2048,输出数据为12位二进制补码。

2.5参考电压

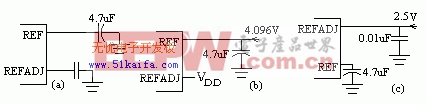

MAX1270可使用芯片内的4.096V参考电压,也可使用外部参考。图2是使用片外参考和片内参考时相关管脚的接法。

图2 管脚连接图 (a) 使用片内参考电压 (b)、 (c)使用片外参考电压 |

3. 电路硬件连接与软件编程

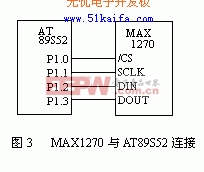

MAX1270与AT89S52的连接方法如图3所示。下面是用汇编语[2]言编写的一个通道AD转换子程序adconversion,外部时钟模式,转换方式25SCLK/s。控制字在R1中。转换所得12位数据高4位放入R3,低8位放入R4。

评论