J-FET开关电路工作原理

1、简单开关控制电路

本文引用地址:https://www.eepw.com.cn/article/187981.htm图5.4-97为简单J-FET开关电路。当控制电压VC高于输入电压V1时,VGS=0,J-FET导通,传输信号至VO;当VC比V1足够负,VD导通而J-FET截止,VO=0。

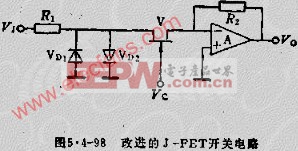

2、改进的J-FET开关电路

图5.4-98电路是图5.4-97电路的改进,增加一级运算放大器以克服J-FET内阻较大的缺点。电路中R1使J-FET上的压降较小,即VD≈VS=0。当VC=0时J-FET导通而与V1大小无关;当VC比夹断电压稍负时,J-FET截止,由于VD1或VD2导通,漏极电位被钳在±0.6V。R1的阻值视V1的幅值选定。运算放大器将传输信号倒相。

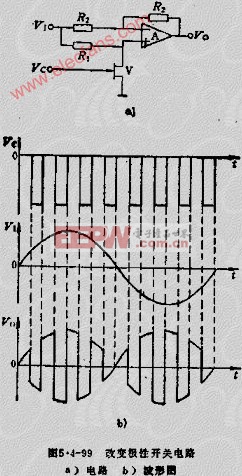

3、改变极性的J-FET开关电路

图5.4-99A所示电路为可改变极性的放大电路。电路应使R1远大于J-FET导通电阻而远小于J-FET的截止电阻,即RONR1ROFF(对漏和源而言)。当VC=0时,J-FET导通,电路为反相跟随器,VO=-V1;当VC比V1最低幅度还低时,J-FET截止,R1上无电流,运算放大器同相输入端电位FIN+=V1,由于反馈,反相输入端电位VIN-=V1,R3上亦无电流,则V0=V1。R1不一定与R1相等或匹配,如果运算放大器输入阻抗很高,R1可选大些。图5.4-99B示出了一种通过该电路的信号波形。

评论