一种AES密码算法的硬件实现

2.4 密钥扩展模块的设计

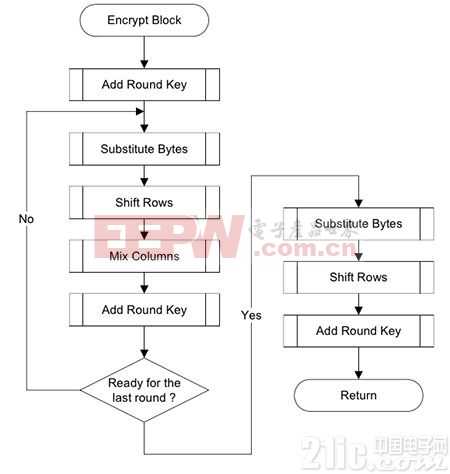

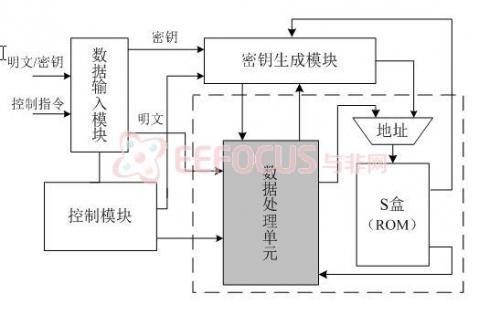

轮密钥的产生是AES加解密运算的基础,密钥扩展模块的作用就是产生除了初始密钥本身之外的10个轮密钥,分别用于10轮加解密运算。

加密运算采用密钥内部扩展的方式,即加密运算与密钥扩展并行完成。这一过程,每一轮变换都要和相应密钥扩展轮次生成的子密钥进行异或,因此需使用状态机控制加密运算和密钥扩展的同步,否则会发生混乱。需要指出,使用内部扩展方式可以提高整个加密运算速度。而解密运算采用外部扩展方式,即密钥扩展完之后再进行解密运算,因为解密运算使用的初始密钥是密钥扩展生成的最后一轮子密钥。

3 仿真测试与结果

根据前述设计思路和优化措施,系统采用Mentor公司专门为各逻辑器件制造厂商设计的第三方专用仿真工具ModelSim 6.o进行功能仿真,给出了最后的功能仿真图。

3.1 加密运算的仿真测试

一次完整的加密操作,需要12个时钟周期。其中,10个周期用于10个轮循环变换,1个时钟周期用于初始的密钥扩展,1个时钟周期用于密文的输出。加密运算的功能测试仿真波形如图3所示。本文引用地址:http://www.eepw.com.cn/article/187767.htm

从图3给出的加密运算功能仿真结果可以看出,加密运算与密钥扩展过程是并行进行。当“rst”变为低电平,“ld”变为高电平时,明文3243f6a8885a308d313198a2e0370734与密钥2b7el5l628aed2a6abf7158809cf4f3c分别同时加载到加解密运算模块与密钥扩展模块中;在下一个时钟周期,密钥扩展模块生成1轮子密钥,等待加密轮变换中的密钥加操作。当完成1次加密过程后,“done”信号变为高电平,同时输出密文3925841d02dc09fbdc118597196a0632。从图3中同时也可以看出,密钥扩展模块总是提前一个时钟周期生成下一轮的子密钥,这样可以保证密钥扩展与加密运算同时进行而不会发生错乱,并且还可提高加密速度,节约资源占用和减少面积。使用DC进行综合和优化后,加密运算模块面积不超过20 000个等效门,其中组合逻辑面积为14 264门,非组合逻辑面积为3 878门。

3.2 解密运算的仿真测试

在解密过程中,完成一次解密操作同样需要12时钟周期。其中,10个周期用于10个轮循环变换,1个时钟周期用于初始密钥的加载,1个时钟周期用于密文的输出。在解密过程中,本文采用在解密之前所生成的10轮子密钥,因为解密初始需要的子密钥是密钥扩展得到的最后一轮子密钥,而最后一轮需要的子密钥是密钥扩展的初始密钥。如图4所示。

解密过程与密钥扩展过程不是同步的,当“kld”为高电平时,从第1个时钟周期开始,便将初始密钥2b7e151628aed2a6abf7158809cf4f-3c输入到密钥扩展模块中,之后经过10个时钟周期生成10轮子密钥,并存储到寄存器中。当“ld”为高电平时,密文3925841d02dc09fbdcll-8597196a0632开始加载到解密模块中,经过10个时钟周期将解密的密文输出,同时“done”信号变为高电平,表示解密过程结束,并输出明文3243f6a8885a308d313198a2e0370734。

对比图3与图4仿真测试结果可知,加解密运算的功能正确,即解密运算能够正确地解出加密运算的密文。解密运算模块使用DC进行综合和优化后面积不超过25 000个等效门。其中组合逻辑面积为10 495门,非组合逻辑面积为14 142门。由于密钥扩展与解密过程不是同步进行,占用了寄存器存储解密过程所需的10轮子密钥,所以非组合逻辑面积比加密运算模块大。但需要指出,由于加/解密运算模块部分电路采用复用的方法实现,所以整个加/解密运算模块的实际总面积比没有复用时减小。

4 结语

根据设计思路和优化措施,本文使用Verilog硬件描述语言实现AES密码算法,并在ModelSim 6.O工具下进行仿真,证明本文设计的正确性。为了更进一步做比较,证明本文设计思路的合理性和优化措施的有效性,同样采取未优化的设计方案实现了该算法,通过在Dc中进行综合、布线,两相比较,优化后的设计比优化前节省了22%的逻辑单元,处理速度提高了13%。

评论