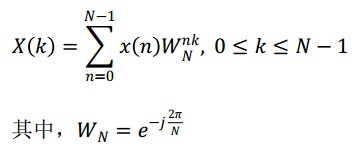

- 随着快速傅里叶变化(FFT)在信号处理应用领域的广泛应用,不同场合对硬件实现的 FFT 算法结构提出了多样化的要求,针对这种需求在硬件编程设计中将 FFT 分割成模块化的三部分:数据存储重排模块、旋转因子调用模块、蝶形运算模块。通过时序调用可组成不同结构的 FFT 处理器,实现流水结构与递归结构两种方案,分别侧重于处理速度与资源占用量两方面的优势。在FPGA硬件设计中使用 Verilog 语言完成代码编程,实现了两种结构的 512 点基 2 算法的快速傅里叶变换,使用 Modelsim 完成功能仿真。与

- 关键字:

FFT 硬件实现 基 2 算法 模块化设计 流水线结构 递归结构 201902

- 摘要:针对脉冲耦合神经网络(PCNN)具有神经元脉冲同步激发、适合硬件实现的特点,提出了一种基于FPGA的PCNN实时处理系统。系统设计了时钟分频、串口

- 关键字:

脉冲耦合神经网络 硬件实现 FPGA 图像处理

- 硬件的设计必须要实现对动力电池组的合理管理,首先必须保证采集数据的准确性;其次是可靠稳定的系统控制;最后...

- 关键字:

锂电池 硬件实现

- 介绍了RBF神经网络,并采用CORDIC算法实现了其隐层非线性高斯函数的映射。同时,为缩减ROM表的存储空间并提高查表效率,本设计还采用了基于STAM算法的非线性存储。最后,以Altera公司开发的EDA工具QuarlusⅡ作为编译、仿真平台,采用Cyclone系列中的EP1C6Q 240C8器件,实现了RBF神经网络在FPGA上的实现,并以XOR问题为算例进行硬件仿真,得出仿真结果与理论值一致。

- 关键字:

FPGA RBF 神经网络 硬件实现

- 针对高清图像在中值滤波预处理过程中排序量多、速度慢的特点,提出适合邻域图像并行处理机的分块存储方法。在流水线结构下,1个时钟周期可以并行处理32个3×3邻域的中值滤波运算,实现了高速、实时的1 920×1 080灰度图像中值滤波器。

- 关键字:

FPGA 中值滤波 硬件实现

- 设计了一种基于FPGA的1024点16位FFT算法,采用了基4蝶形算法和流水线处理方式,提高了系统的处理速度,改善了系统的性能。提出了先进行前一级4点蝶形运算,再进行本级与旋转因子复乘运算的结构。合理地利用了硬件资源。对系统划分的各个模块使用Verilog HDL进行编码设计。对整个系统整合后的代码进行功能验证之后,采用QuartusⅡ与Matlab进行联合仿真,其结果是一致的。该系统既有DSP器件实现的灵活性又有专用FFT芯片实现的高速数据吞吐能力,在数字信号处理领域有广泛应用。

- 关键字:

FPGA FFT 算法 硬件实现

- 介绍了一种适用于较小面积应用场合AES密码算法的实现方案。结合该算法的特点,在常规轮变换中提出一种加/解密列混合变换集成化的硬件结构设计,通过选择使用同一个模块,可以实现加密和解密中的线性变换,既整合了部分加/解密硬件结构,又节约了大量的硬件资源。仿真与综合结果表明,加/解密运算模块面积不超过25 000个等效门,有效地减小了硬件实现面积,同时该设计方案也满足实际应用性能的需求。

- 关键字:

AES 密码算法 硬件实现

- 摘要:提出了一种完整的降采样FIR滤波器的设计和硬件实现方法。该方法首先利用matlab工具箱自带的FDAtool设计出降采样FIR滤波器的系数,然后采用横向抽头式结构进行硬件实现。硬件实现时,先利用FIR滤波器系数对称的

- 关键字:

FIR 降采样 滤波器 硬件实现

- 摘要:BCH码是一种理论上比较成熟的代数码型,在电力通信系统,GSM标准的语音和数据业务,以及卫星通信和数字广播通信(DVB-S2)等多个领域均有着广泛的应用。基于幂次运算,在线性反馈移位寄存器(LFSR)下实现了基于Be

- 关键字:

BCH 算法 硬件实现

硬件实现介绍

您好,目前还没有人创建词条硬件实现!

欢迎您创建该词条,阐述对硬件实现的理解,并与今后在此搜索硬件实现的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473