功率管理技术介绍

随着由电池供电的便携式消费类产品的增长,IC芯片的功耗已成为了一个世界性的问题,设计者必须通过配置合适的功率管理系统采用各种办法来节省能量。便携产品的设计却要求工程师开发更有效的节能系统。随着消费类产品越来越复杂,功率管理系统的设计也越来越复杂。

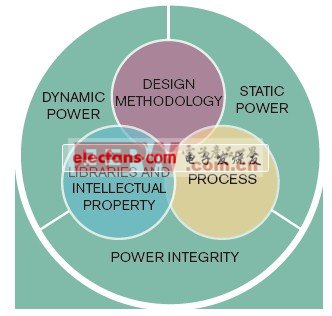

本文引用地址:https://www.eepw.com.cn/article/185728.htm对于移动设备而言,更长的电池使用寿命、更长的通话时间或更长的工作时间都是明显的优势,降低电源要求意味着使用体积更小的电池或选择不同的电池技术,这在一定程度上也缓解了电池发热问题;对于有线系统而言,设计师可通过减小电源体积、减少冷却需求以及降低风扇噪声来提高电池效率。有效的功率管理涉及到恰当技术的选择、优化的库和知识产权(IP)的使用,以及设计方法(图1)。

图1,有效的功率管理需要选择恰当的技术、库和IP设计方案以及芯片设计方法。

功耗在电子设备中正变得更加重要。功率的损耗。电路中通常指元、器件上耗 散的热能。有时也指整机或设备所需的电源功率。 功耗同样是所有的电器设备都有的一个指标,指的是在单位时间中所消耗的能源的数量,单位为W。不过复印机和电灯不同,是不会始终在工作的,在不工作时则处于待机状态,同样也会消耗一定的能量(除非切断电源才会不消耗能量)。

MOS晶体管的基本工作

为了解功率,让我们从经典的MOS晶体管漏极电流方程开始,MOS晶体管是一种新型MOS与双极复合型器件。它采用集成电路工艺,在普通晶闸管结构中制作大量MOS器件,通过MOS器件的通断来控制晶闸管的导通与关断。虽然这些方程只对较老的技术准确,并且未考虑现代技术中的亚微米几何结构引入的各种影响,但它们使人们能了解晶体管的总体行为。

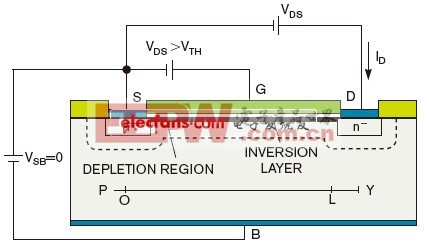

图2,某NMOS FET表明了施加在其端子的电压。

在数字电路中,当晶体管处于接通状态时,它位于饱和区,此时漏极至源极电流IDS服从以下方程(图2):

(1)

其中TOX是栅极氧化物厚度,W是晶体管的沟道宽度,L是晶体管的沟道长度,VGS是晶体管的栅极与源极之间的电压,VTH是阈值电压,K取决于工艺技术。阈值电压服从以下方程:

(2)

其中VSB是源极与基底之间的反向偏压,VFB是平带电压(它取决于工艺技术),γ和ΘS也是取决于工艺技术的参数。

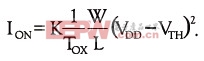

如果漏极至漏极电压等于电源电压,即栅极与源极之间的最大电压,那么你就能运用以下方程来计算接通电流:

(3)

然后可以把有功功率表示为:

(4)

泄漏功率

MOS晶体管中的主要泄漏部分是结泄漏、栅极泄漏、栅极感应漏极泄漏、亚阈值导电。当漏极和基底之间或是源极和基底之间的PN结在晶体管处于关断状态下变成负偏压时,会出现结泄漏,此时由于存在反向偏压二极管而出现泄漏电流。

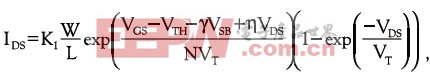

当栅极至漏极重叠区中的高电场导致带至带隧穿,并导致栅极感应漏极泄漏电流时,就会出现栅极感应漏极泄漏。当晶体管处于关断状态时,会出现亚阈值导电;它并非真地处于关断状态,但由于微弱的反相而导电。亚阈值导电是导致泄漏电流的主要因素。你可把该电流表示为:

(5)

评论