基于全耗尽平面晶体管技术的NovaThor平台设计

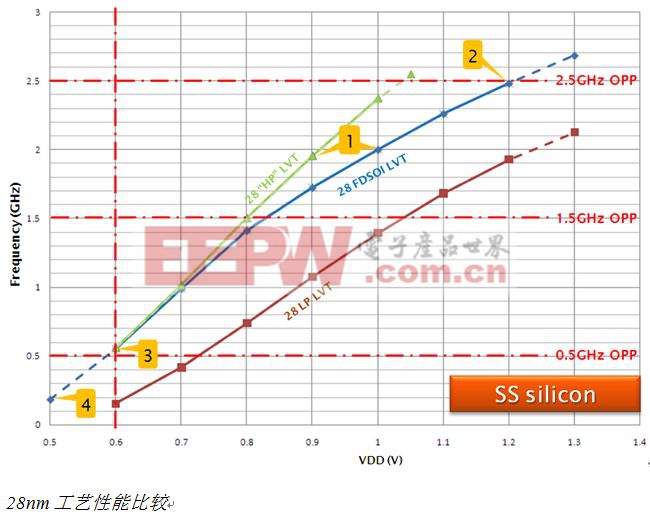

随着智能手机功能最近不断升级演化,消费者的期望值日益攀升。速度更快的多核高主频CPU处理器、令人震撼的3D图形、全高清多媒体和高速宽带现已成为高端手机的标配。同时,消费者还期望手机纤薄轻盈,电池续航能力至少与以前的手机持平。对于手机厂商和设计人员来说,消费者的期望意味着移动芯片需具备优异的性能,同时兼具低成本和低功耗。全耗尽平面晶体管技术 (FD-SOI:Fully Depleted Silicon on Insulator),是满足这些需求的最佳解决方案。 在2012年移动通信世界大会上(Mobile World Congress),意法。爱立信首席执行官Didier Lamouche证实我们的下一代NovaThor平台,即NovaThorL8540的后续产品,将采用28nm FD-SOI制造工艺。 FD-SOI技术目前已经可供芯片开发使用,该技术将会使28nm工艺制程的芯片产品在性能和功耗方面有显着的提升。因为工艺复杂程度相对较低,FD-SOI解决了制程升级、泄漏电流和可变性等问题,能够将CMOS制程节点进一步降至28nm或28nm以下。 像FinFET技术一样,FD-SOI最初是为20nm节点及以下开发设计的,能够突破传统体效应CMOS制程升级的限制因素,例如,高泄漏电流和终端设备多样性的难题;但是,又与FinFET技术不同,FD-SOI保留了传统体效应CMOS工艺的平面结构复杂度相对较低的优点,这可加快工艺开发和量产速度,降低现有设计的迁移难度。意法爱立信、意法半导体、Leti 和Soitec的技术合作让我们能够在28nm技术节点发挥FD-SOI的优势:先进性能、具有竞争力的处理速度/泄漏电流比和优化能效。 在宽电压范围内性能领先 下图比较了在慢工艺角(SS)和环境温度最恶劣时ARM Cortex-A9 CPU内核的一个特定关键通道能够达到的最高频率-Vdd电源电压曲线。 每条曲线代表一个特定的28nm制程: .28HP-LVT是用于移动设备的高性能体效应CMOS工艺,瞄准高性能移动设备CPU,具有处理速度快和栅极氧化层薄的特点,因此,从可靠性看, Vdd 过驱动能力有限(~1.0V)。 .28LP-LVT 是一种低功耗的体效应CMOS 工艺,过去用于低功耗移动应用,LP 基于栅氧化层更厚的晶体管,支持更高的过驱动电压(高达1.3V)。 .28FDSOI-LVT是意法半导体开发的28nm FD-SOI工艺,栅极结构与28LP相似,也支持1.3V过驱动电压。 在这三种工艺中,只考虑低压阈值(LVT),因为处在这样的电压下时处理性能最高。 1.首先观察到的是,在标称电压(HP=0.9V,LP=1.0V,FD-SOI=1.0V)时,FD-SOI的峰值性能与HP工艺相似;在Vdd电压相同时,性能比LP高35%. 2.此外,随着Vdd 电压升高,FD-SOI的性能进一步提高,而 HP 工艺无法承受更高的电压,因此,前者的综合峰值性能高于后者。 3.在工作电压过低时,如Vdd=0.6V, LP将无法运行或性能很低;FD-SOI与HP工艺相当甚至高于HP工艺,但是前者的泄漏电流和动态功耗要比后者低很多,我将在后面的内容中给予说明。 4.相比体效应CMOS工艺,FD-SOI的工艺可变性低,在适合CPU处理非密集型任务的频率(200MHz-300MHz)时,能够支持更低的工作电压(最低0.5V),例如,硬件加速音、视频播放。

评论