高可靠性的可编程电源管理解决方案

系统工程师正受到降低成本和提高电路板可靠性的压力。一个经常被忽视的应对措施是减少为FPGA、 微处理器和数字信号处理器进行电源监控而使用的元件数量。新颖的高集成度可编程电源电路将复位生成电路、看门狗定时器(WDT)和电压.集成电路集成在单个器件之中。这种一体化方案有助于降低系统成本,解决设计人员所关心的可靠性问题。本文讨论将可编程逻辑、ADC和DAC集成在一起的创新解决方案,该方案使电源管理功能具有更高的精确性,同时还可降低成本。

本文引用地址:https://www.eepw.com.cn/article/181139.htm电源管理的挑战

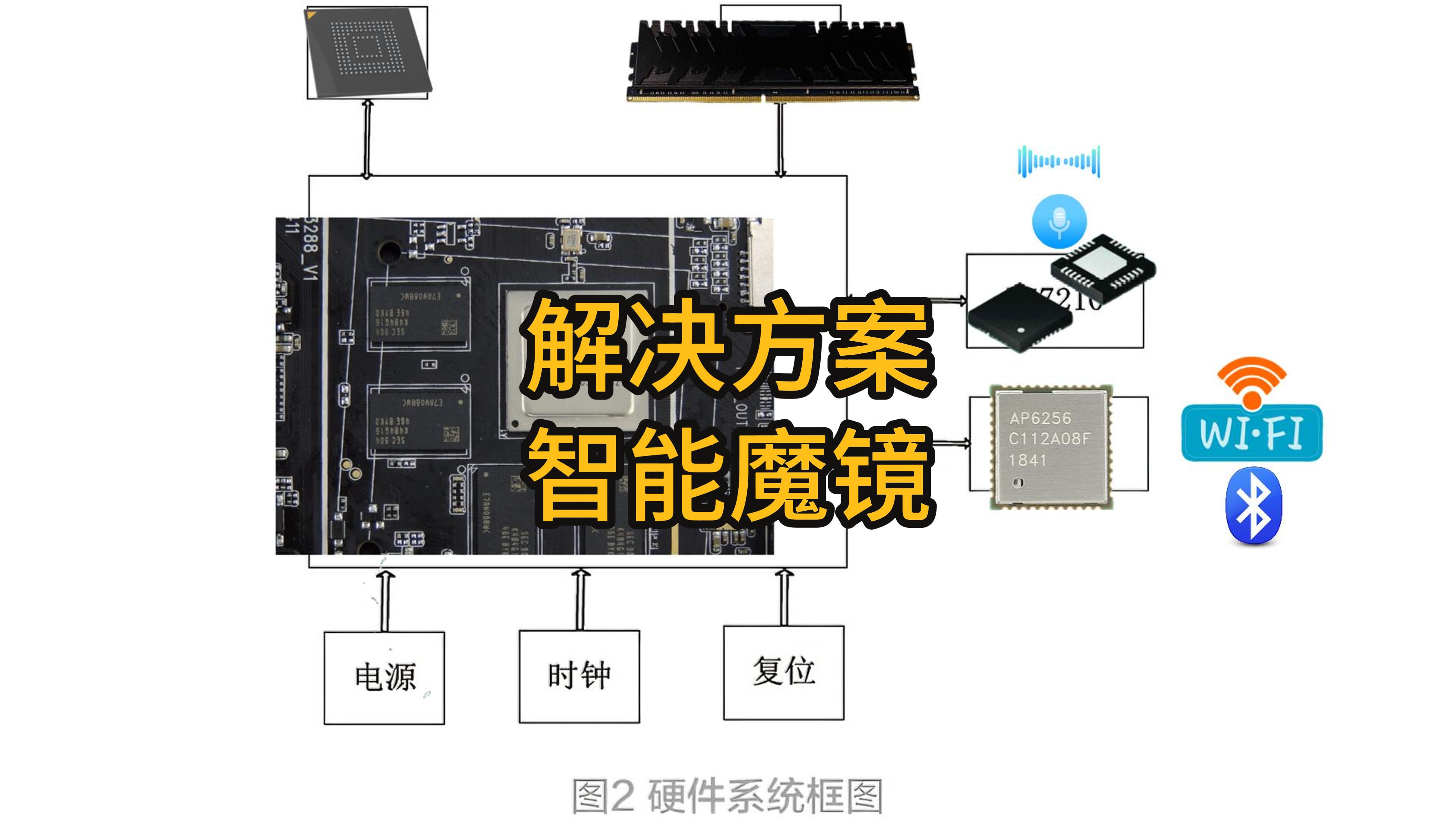

一个典型的CPU电源电路如图1所示。对于典型的DSP、 FPGA或微处理器,各种电源电压要求为:器件的核心电压为1.2V、辅助电压和PLL电压为3.3V、 I/O驱动电压为1.5V和1.8V。常见的电源设计的电压是源于单一的5V输入电源,通过一系列DC/DC转换器后产生各种电源电压。为提供如同单电源印刷电路板一样的可靠性,必须对电路板上的所有电源进行监测,并能产生正确的CPU复位信号或电源故障中断信号。

图1的电压监控块是一个集成电路,当电源发生故障或手动切断电路板的电源时,它会发送信号给CPU。如果任何一个DC/DC转换器发生故障,电压将升高或降低,超出正常工作电压的范围,从而导致CPU不能正常执行程序。对CPU而言,一个潜在的最糟糕情况是非易失性内存被改写,使系统无法启动。如果电源发生故障时能够中断CPU,就能安全地中止当前任务,为可靠重新启动保存重要信息。

许多廉价的电压.集成电路通常有一个被忽视的负作用,对于电压变化,.的阈值将影响整个系统的容差。图2说明了这种情况。核心电压的规格为1V+/-5%,如果CPU核心电压低于0.95V,就要求.必须发出一个中断信号。然而,考虑到.的阈值精度,电压变化的整个容差降低了。在这个例子中,该.的阈值为0.95V+2%/-3%(0.97V至0.93V)。采用这种监控集成电路时,该阈值应设置成0.97V ,这就限制了DC/DC转换器的容差。

图1中的复位发生器块是另一种较常见的分立集成电路,当所有电压稳定后,它向CPU发出释放复位输入信号。在所有电源稳定之后,CPU继续保持复位模式一段时间是常见的情况。例如,Power Good信号有效后,移动式英特尔Atom处理器期待“脉冲延伸”两个毫秒的复位脉冲。只有到那个时刻,CPU才开始执行程序。

评论