贯穿整个IC实现流程的集成化低功耗设计技术

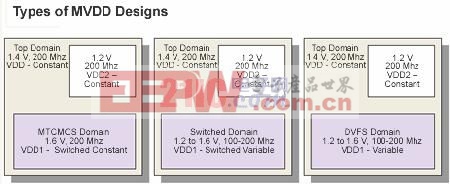

其中一项标准技术是将设计分为大量“电压岛”(图2)。虽然供电电压较低的电压岛,其性能也就较差,但其动态功耗也将大幅降低。

图2. 多电压域(multi-Vdd)设计类型。

在将设计分为多个电压岛时,信号从一个电压域到另一个电压域传输必须要插入适当的电压转换器或隔离元件。一个真正有功耗意识的设计环境应该能够自动插入这些单元并做好其验证工作。

由电压岛和降频技术所组成的动态电压和频率缩放(DVFS)是最先进的一种降低动态功耗方式。系统可被设计为各个功能块按照不同的电压和频率组合工作,随着器件的操作模式变化而变化。这就是为什么多核处理器能具有长待机的电池寿命和高效的按需计算能力的原因。

静态功耗

在当今的工艺技术中,不工作时元器件的漏电流是个大问题。这种电流与温度和开关阈值成指数关系,给功耗优化工作带来了很大困难。

解决静态漏电问题的一种方式采用具备多阈值电压(Vt)元器件的库,在设计中一部分使用低阈值晶体管,其它部分则使用高阈值晶体管,不过这只能解决部分问题。其中低阈值晶体管开关速度较快但漏电流较高、功耗较大;而高阈值晶体则开关速度较慢但漏电流较低、功耗较小。

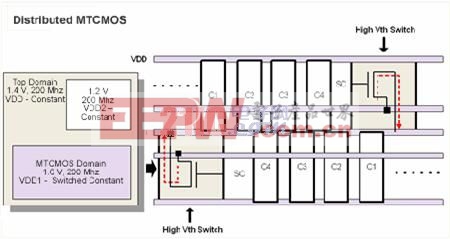

还有一种方式是利用高阈值电压(high-Vt)开关来有选择地切断设计中未工作部分的电源。利用高阈值电压开关来连接全局恒定电源线轨与局部开关电源线轨,让局部线轨的电源根据需要开启或关闭,这就提供了对功率门控的细粒度、中粒度和粗粒度的控制能力(如图3)。

图3. 多阈值CMOS晶体管能被用于功率门控,通过提供对局部电源导轨的细粒度控制从而降低功耗。

不过,所有这些方式都必须与功率分布网络设计工作同步进行,而不是在设计流程后期单独进行。首先,早期线轨分析必须在电源网格还未完成时执行,这样耗能元件才可均匀地分布在芯片中,避免热点和局部电压降问题。其次,要有选择地使用线宽算法来解决电压降和电迁移问题。当然,这些技术都要求有早期集成化分析。

评论