贯穿整个IC实现流程的集成化低功耗设计技术

降低功耗是现代芯片设计最具挑战性需求之一。采用单点工具流程时,往往只有到了设计流程后期阶段才会去考虑降低功耗的需求,从而经常导致大量问题和延时。微捷码设计自动化有限公司高级技术产品经理Rob Knoth向我们解释了‘为何功率优化应是完整设计流程必不可少的集成组件’。

本文引用地址:http://www.eepw.com.cn/article/180912.htm起初,低功耗设计技术主要是用于移动产品。而今插在电源插座上的产品数不胜数,它们都在不断吸收着电流,全世界大量功率都浪费在了这些产品上。今天,政府正积极要求电子企业遵从更严格的要求来帮助降低全球功耗。低功耗设计与每个人息息相关。现在低功耗需求无处不在,而且变得更具挑战性。

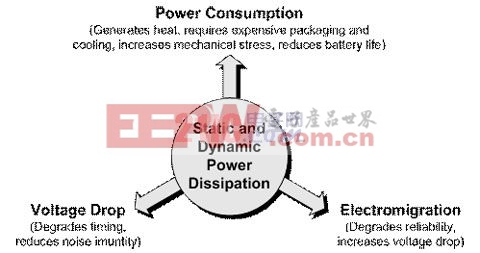

低功耗设计,不论是动态功耗还是静态功耗,均要求设计流程各个阶段时序、功耗和面积间复杂的折衷权衡。这些需求相互间联系密切,要想解决这些需求,低功耗分析和优化引擎必须集成并运用于从RTL规格到GDSII输出的整个流程中。由于芯片尺寸还在持续增长,因此这一流程必须是可缩放的,否则它将会对设计师工作效率造成限制。

图1: 低功耗设计牵涉到设计流程的各个方面

动态功耗

设计的动态功耗是由电容、电压和频率共同决定的。

电容主要受到门极电路尺寸及布线的影响。逻辑门尺寸是降低内部开关电流与增加系统面积、噪音和容性负载间的一种折衷权衡。缩短布线将意味着容性负载的减少,但是带来拥塞情况的恶化,可能导致布线违规或源自串扰的时序问题。

频率对系统动态功耗的影响很大。采用并行处理方式,系统时钟可以降低,同时保持吞吐量不变。当然这是以牺牲面积为代价,是从架构上进行考虑。

在芯片总功耗中,时钟树网络的功耗占据了很大一部分。将功耗作为一个成本函数来考虑已变得越来越重要,特别在较小尺寸中更是如此。目前已有各种不同技术可被广泛应用于RTL综合和物理综合中,如:广泛的门控时钟覆盖、门控时钟克隆/反克隆、有功率意识的缓冲器插入、尺寸调整和门控时钟布局。此外,如时钟树综合(CTS)中多阈值电压(Multi-Vt)、层次化时钟门控、基于行为的时钟门控等其他技术也可以提供额外的功率节省。门控技术降低动态功耗也必须在面积和静态功耗上平衡折中。

评论