微处理器的电源管理方案

随着领先微处理器的每一代后续产品对电流的需求不断提高,为了使功耗保持在可管理的水平,就需要把工作电压降至更低。同时,这些高电流水平带来极大的电流变化率(di/dt),因而使电压调节(即稳压)也变得更加困难得多。了为缓解这一问题,稳压容差指标一直在不断下降。5年前,±250mV还是可接受的;到2005年,任何微处理器供电电源的最大稳压容差将不得超过±25mV。

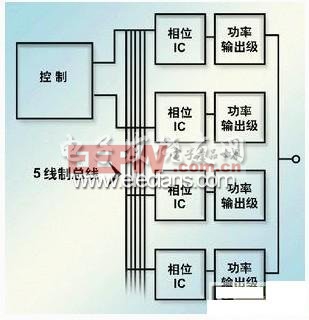

本文引用地址:https://www.eepw.com.cn/article/178619.htm展望2005年的先进微处理器,预计未来电源供电解决方案的电流水平将从目前的60A增至130A,同时电压将下降到1.1V。这已带来够大的挑战,但更苛刻的要求将接踵而来,即如何在满足800A/usdi/dt的条件下,实现±25mV的稳压。更多的相位将在多相、点负载(point-load)型转换器中被采用,而频率将从目前的500kHz不断增加至2005年的2MHz。此外,保持目前每安培成本水平的压力会一直存在。从整体来看,微处理器为DC/DC转换器设计带来的挑战包含了许多技术、涉及许多领域内的专门知识。为取得成功,厂商必须拥有达到基准水平的功率硅片功能;其次,封装方案绝对要是一流的;另外,有创意的控制IC方案必不可少。最后还必须采用一个先进的电源架构将所有这些整合到一起。

功率硅片

在功率硅片领域,为了满足未来几年微处理器将提出的预期要求,像国际整流器公司(IR)等电源管理行业的主导厂商已经取得了长足的进步。

图1所示的是开关品质因数(FOM),这是评判降压拓扑结构中控制场效应管(FET)或称高端(high-side)FET性能的一个典型方法。通过从1至2微米平面拓扑结构变为为亚微米沟道,开关品质因数被提高了1-3倍多。图2所示的是同步或称低端(low-side)FET的品质因数。在这里,实际上是传导损耗主宰了处在导通电阻时域的品质因数。仅在过去的两年中,通过将1至2微米沟道技术升级为深亚微米水平,就使品质因数提高了约3倍,今后还有更多的改进余地。

为满足未来几年内微处理器的需求,业界需沿着这条改进之路继续前行。对控制FET来说,通过转向更细的线路和横向(lateral)拓扑结构,品质因数可获得另一次3倍的提升。在同步FET领域,在硅沟道技术中采用越来越细的线路几何结构还可再次获得2.5倍的提升。在更远的将来,为了与雄心勃勃的发展规划同步,业界将需要采用诸如金刚砂和氮化镓这样的替代材料。否则,功率半导体器件的进步将不足以满足未来微处理器的要求。

创新的封装

在某些方面,封装本身已成为取得进步的障碍,如SO-8的例子。该封装是迄今为止用于面向微处理器的点负载转换器的最流行封装形式。SO-8带有1.5毫欧的封装阻抗(DFPR),能被装入其中的硅片其阻抗要小于该封装阻抗。SO-8还在热阻方面表现欠佳,向下至PCB板、向上到空气散热(18℃/瓦)两个方向均是如此。

为了解决这些问题,一些新型封装已被开发出来,如IR公司的PowerPak,以改善DFPR和热阻问题。可解决这些问题的其它封装方面进展也层出不穷,例如:铜带(copperstrap)、LFPak以及无底座SO-8等。尽管如此,业界还必须开发其它一些新颖的封装方法以进一步改进热阻性能。其中一种前景看好的新型封装技术是将热量向上推,然后将其释放到电路板上方的空气中,而不是将热量向下压进已在吸收若干其它元件发热的PCB板。为将硅片所占面积和阻抗降至最低,这种新型的DIRectFET封装采用一个铜“顶帽”,以便与上下双向热通道建立起机械强度很高的连接,从而极大地改善了DFPR和两个方向上的热阻问题。该设计有效地使板上功率密度得到双倍地增加。

评论