基于电荷泵锁相环的有源环路滤波器的设计

摘要:环路滤波器是锁相环中的一个关键模块,对宽带高压VCO进行调谐时,常采用有源滤波器。在论述了电荷泵锁相环基本原理的基础上,对有源环路滤波器的结构以及滤波器对锁相环性能的影响进行了分析,推导出有源环路滤波器参数的设计方法。根据课题设计了三阶有源环路滤波器,用ADS工具对锁相环系统性能进行仿真,仿真结果与理论相吻合。实验结果表明,所设计的滤波器满足了课题的要求,验证了本方法的正确性。

关键词:电荷泵锁相环;有源环路滤波器;相位裕度;环路带宽

电荷泵结构的锁相环(CPLL)具有易于集成、低功耗、无相差锁定、低抖动等优点,因而得到广泛应用。环路滤波器(LPF)是电荷泵锁相环电路的重要部分,其决定了锁相环的基本频率特性。由于有源器件会引入的相位噪声,因此一般情况下采用无源滤波器作为环路滤波器。但是对宽带高压VCO调谐时,须采用有源环路滤波器以提供较高的输出电压。通常有源环路滤波器常选择二阶以上,采用多阶极点可以改善有源滤波器的性能。此外,高阶环路滤波器可在保证相同的鉴相杂散抑制的同时,可以允许更宽的环路带宽和更高的鉴相频率,降低了分频比,从而改善锁相环的带内相位噪声性能。因此,研究有源环路滤波器的设计有着重要的意义。

1 电荷泵锁相环基本原理

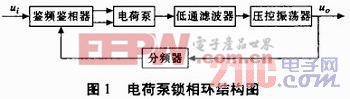

电荷泵锁相环结构如图1所示,包括鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器。鉴频鉴相器比较两个信号的相位与频率差,并产生控制信号给电荷泵,然后电荷泵相应地给环路滤波器充放电,此时压控振荡器输出频率正比于环路滤波器上的控制电压,最终使参考时钟fr与分频器的输出信号同频同相,即压控振荡器的输出信号频率f0为参考时钟频率的N倍。

即 f0=NFr (1)

如果输入信号的带宽为Br,那么最终得到的输出信号带宽B0为参考源输入带宽Br的N倍。

即 B0=NBr (2)

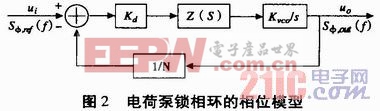

电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在PFD的鉴相范围内时,可以采用线性近似。那么当电荷泵锁相环处于相位锁定过程时,就可得到一个线性连续时间相位模型,如图2所示。

其中Kd是PFD和电荷泵一起构成的鉴相器增益,并有Kd=Icp/2π,Icp为电荷泵的充放电电流,kvco为压控振荡器的增益,N为分频器的分频比,Z(s)为环路滤波器的传输函数。设计中锁相环路起到了倍频的作用,参考输入的噪声由于倍频而恶化。

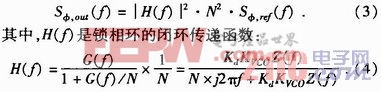

Sφ,ref(f)为参考输入的噪声功率谱密度,Sφ,out(f)经过锁相环路倍频后输出噪声功率谱密度,根据信号理论,可得:

开环增益G(f)=KdKvcoZ(f)/2π是在频域上单调递减,因此|H(f)|呈现低通特性,低通截止频率为fc,等于锁相环的环路带宽。在环路带内较小的偏离频率范围ffc处有|H(f)|≈1,此时参考输入噪声影响锁相环输出信号的相位噪声。从公式(3)中,可知参考信号输入的相位噪声与杂散由于锁相环路倍频而恶化20lgN(dB),因而分频比不宜过大,而较低的分频比也意味着更高的频率分辨率和改善的锁定速度;另一方面,当分频比较低时,DDS的输出频率带宽需要足够大,这必然会增大输出杂散和相位噪声。

2 有源环路滤波器的设计

通常用于锁相环的有源环路滤波器包括简单增益型和反馈型两种,在实际工程中多采用简单增益型,常见的为二阶和三阶滤波器。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

分频器相关文章:分频器原理 电荷放大器相关文章:电荷放大器原理 光伏发电相关文章:光伏发电原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论