高斯噪声源电路的设计与实现

摘要:为了实现占用资源少、精度高的高斯噪声源电路,设计了一种新的高斯噪声产生方案,该方案在FPGA上通过线性反馈移位寄存器产生高速均匀分布伪随机数,接着利用均匀分布与高斯分布之间的映射关系生成高斯噪声,并创新地采用非均匀划分的折线逼近映射曲线,同时设计寻址电路,从而减少噪声源占用的资源,改善噪声精度。在XILINX Virtex5 XC5VLX50T上的实现结果表明,该方案仅使用了2%的可配置SUCE和1块片上BRAM,实现了+4σ(σ为标准偏差)的高斯噪声源。时序分析表明其最高频率可达131 MHz。

关键词:高斯噪声源电路;查表法;非均匀划分;寻址电路

在硬件实现的跟踪系统中,经常需要高斯噪声信号源来提供噪声。传统的高斯噪声大多在基于DSP的软件系统上生成,其产生速度比硬件系统工作频率要慢很多,且不利于SOC(system on chip)的集成。通常,在这样的系统里有大量的运算与逻辑操作(例如,硬件粒子滤波系统)高斯源作为噪声模块只是很小的一个功能块,因此设计时需要尽量减少噪声源占用的资源,以便将有限的FPGA的资源尽量留给其他计算模块。然而,噪声的精度却对最终的跟踪结果精度有着直接影响,因此要想获得高精度的跟踪结果必须改善噪声的精度。为了获得占用资源少、精度高的高斯噪声源电路,设计了本文的高斯噪声产生方案。该方案由Verilog HDL编程,可移植性强,可作为功能模块移植到其他系统中产生高斯噪声。

1 方案选择

为了获得高斯噪声,通常采用数字合成方法,首先产生均匀分布的伪随机数噪声,然后通过一定的转换方法获得高斯白噪声。

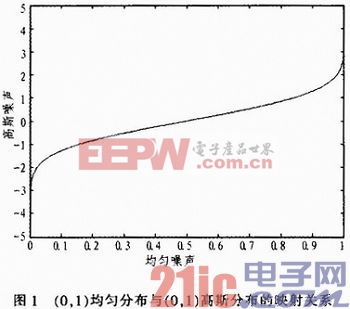

均匀分布的伪随机数产生已经有较长的研究历史,主要的方法有:线性同余法、m序列产生法、logist方程法、进位加方法。FPGA具有并行计算的优势,可以胜任基本逻辑、简单加减法、大小比较、多路选择和时序逻辑等操作。通常FPGA采用查找表实现组合逻辑运算,当组合逻辑过于复杂时,往往需要使用多级查找表来完成运算,大大降低速度,如乘除法。因此用FPGA实现伪随机数发生器,算法应该尽量简单,并尽量不要使用乘除法。考虑到以上因素,本设计采用m序列产生法,该算法具有简单、产生速度快、可重复性强的特点,并且得到的伪随机序列周期较长。将均匀分布的随机序列转化为高斯分布的随机序列的方法主要有函数变换法、中心极限法、查找表法3种。前两种方法都使用到了复杂的运算,在FPGA上实现时需要占用较多的逻辑资源。查找表法通过图1所示的均匀噪声和高斯噪声之间的映射关系建立查找表,通过查表方法得到对应高斯噪声。若对每个均匀输入都建立查找关系,则对于n位的均匀噪声输入需要建立2n大小的查找表,查找表大小随着输入位数增加成指数增长。当为了增加精度而提高n时,查找表大小迅速增长到不能接受。文献利用折线来逼近映射曲线,查找表里存储折线的偏移和斜率,从而减少查找表的大小。观察图1发现曲线在高斯噪声绝对值小的地方斜率小,在绝对值大的地方斜率大。如果采用均匀量化的方法,则在高斯噪声绝对值越大的地方精度越差。要想得到更高精度,就要增加均匀量化级数,增大查找表。文中引入非均匀划分的思想,在斜率较小的地方,用较少的折线逼近映射曲线,在斜率大的地方,用更多的折线逼近映射曲线,这样可以在不增加查找表大小的情况下改善精度。

文中的安排如下:在第2节中给出了均匀伪随机数的实现过程。第3节详细描述了本文的非均匀划分的方法和寻址方式。在最后1节,给出了设计结果和结论。

评论