高斯噪声源电路的设计与实现

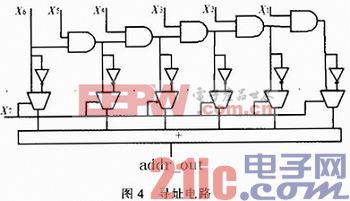

为了对这7段空间进行寻址,设计图4的寻址电路,该寻址电路具有收缩的特性,随着地址增长,2个相邻地址对应的输入x间的距离越来越小。当x7=1时,对应x坐标大于0.5,寻址电路中间部分可以视为通路,电路直接寻址取得直线斜率和偏移后通过计算模块获得高斯噪声输出。当x7=0时,通过多路选择器对寻址做相应变换,同时x7作为控制信号,控制计算模块结果取反。本文引用地址:http://www.eepw.com.cn/article/175995.htm

4 仿真结果

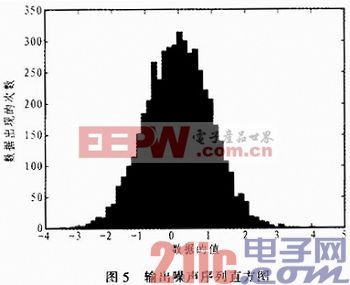

文中采用XILINX公司的Virtex5系列的XC5VLX50T芯片上实现了上述设计,设计主要占用了20%的可配置的SLICE和一块片上BRAM,实现了±4σ的高斯噪声源,将5 000点的输出结果导入到Matlab里并绘制直方图,得到如图5所示。

由图可以看出,生成的噪声序列密度函数基本符合高斯分布,达到了设计要求。

5 结束语

高斯源噪声作为最常用的噪声源之一,经常被应用于各种需要加噪处理的系统和算法。相对于传统的高斯噪声源来说,基于FPGA的非均匀折线逼近的高斯噪声源具有高速、占用资源少、精度高、可移植性强的优点。容易作为IP核,移植到高速的数字系统中。

评论