LMK0480X 产品供电电源设计指导

Anjin Du / Nick Da ---China Telecom Application Team

本文引用地址:https://www.eepw.com.cn/article/174666.htm摘要

本文主要介绍了 TI 的新一代时钟产品 LMK0480X 系列芯片的供电设计以及对时钟性能的影响。通过合理的供电电源电路设计,可以有效地提高芯片性能,降低对供电电源纹波的要求。

1、LMK0480X 供电电路介绍

LMK0480X 系列时钟产品是 TI 近年推出的时钟抖动滤除芯片,采用了两级锁相环级联架构。第一级锁相环主要利用窄带环路滤波器,滤除参考输入(CLKin)的相位噪声和杂散,起到时钟去抖的作用,利用外部 VCXO 产生一个干净的系统参考时钟。第二级锁相环主要是利用第一级输出作为其参考时钟,生成系统所需要的各种时钟频点,同时满足系统设计所需要的相噪、抖动和杂散要求。在实际应用中,外部 VCXO 的选取,环路滤波器的设计以及各种环路参数的优化,都对最终的时钟性能有很大的影响。除这些因素外,芯片的供电设计是应用中需要考虑的另外一个重要部分,不当的设计会直接导致输出时钟不能满足系统的需求,尤其是一些对抖动和毛刺要求较高的应用场景。

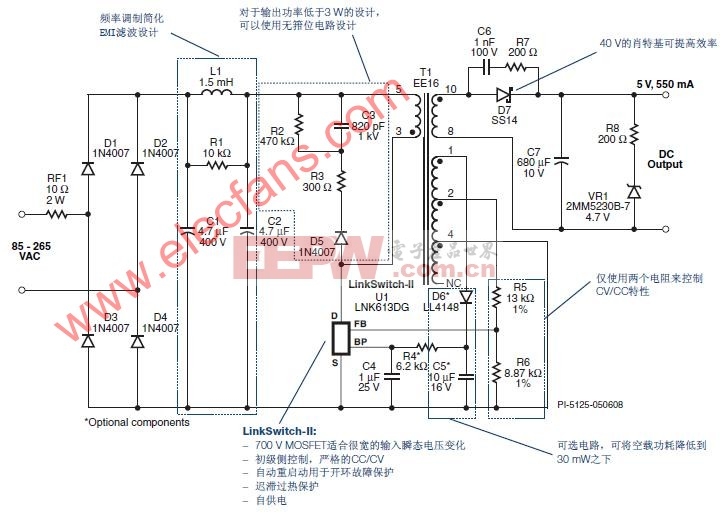

LMK0480X 芯片的供电电源管脚的分布如上图所示,大致可以分为以下几类:

本章中主要整体介绍了 LMK0480X芯片内部模块电路的供电设计。下一章节中将结合实际实验,详细介绍LMK0480X 的供电电源噪声对实际性能的影响。

2、LMK0480X 供电设计和 PSRR 性能测试

2.1 LMK0480X 供电设计原则

针对不同种类的供电管脚,对外部的供电电路的需求不同,一般需要遵循的原则如下:

• LMK048XX 所有的供电管脚内部都有一个集成的高频去耦电容,由于这个电容更加靠近芯片,可以排除封装 bonding 线的寄生电感的影响,去耦的效果比外部的高频去耦电容( 1nF)更有效。同时外部的去耦电容容易将地平面的一些高频干扰引入到芯片的供电管脚,所以一般不建议在 LMK0480X 的所有供电管脚增加 1nF 的去耦电容。

• VCC1,VCC4,VCC9 所负责的芯片内部电路不会产生噪声,所以这三个供电管脚可以连接在一起,共享供电电路;也不需要增加磁珠隔离管脚和总的供电电路,因为磁珠容易影响 VCO 的供电(VCC1),在输出形成鼓包。

• VCC6 和 VCC8 是给前后两级锁相环的电荷泵供电,这对芯片的最终性能至关重要,建议独立的供电支路。对于 VCC6,由于是给第一级锁相环供电,一般第一级锁相环的鉴相频率都比较低,所以供电支路的磁珠可以省去,同时也可直接把 VCC6 直接接入 VCC1/4/9 的电路。而对VCC8 而言,由于为了增加环路带宽,第二级锁相环的鉴相频率比较高(>50MHz),为了防止鉴相频率泄露到其他供电管脚,要求 VCC8 具有独立的供电支路,同时应当增加磁珠以隔离VCC8 和主供电电路的干扰。当鉴相频率较低时,可以考虑去掉这个磁珠。

• VCC5 和 VCC7 主要是给芯片的参考和 VCXO 的输入输出提供电源,同时也给 PLL2 的锁定指示电路提供电源。对于这些管脚,不需要外部的大的去耦电容和磁珠,以防止一些地平面的干扰串入电源管脚,从而影响 PLL2 的锁定指示。

评论