利用ispLSI实现单片机与计算机间的通信

单片机结构简单、开发方便,能够满足各种应用领域的需求,在工业控制及自动化装置中得到了广泛的应用。它既可以单独使用,也可以多片协同工作或作为计算机的信号预处理器,在这种情况下,通信问题就成了限制系统性能的瓶颈。通常使用的通信方式有串行和并行两种,串行方式硬件结构简单但数据传输速率低,不适合大批量数据的传送;并行方式下使用最多的中断方式,以期提高CPU效率。但中断方式也存在不少问题,除了具体的中断服务外,保护、恢复断点和寄存器的内容、查取中断向量等也占用不少CPU时间,如果数据较长,传送一组数据CPU会被多次中断,大量的断点和寄存器的保护、恢复等工作特别影响CPU 效率。为了解决这一问题,本文提出了一种新的通信方式,称之为中断查询方式,并利用在系统可编程逻辑器件 ispLIS1016实现了通信接口。

本文引用地址:https://www.eepw.com.cn/article/172175.htm1 通信原理

中断查询方式的实质是中断方式和查询方式的结合:通信双方由中断方式进入数据传送状态,之后双方在中断内利用查询方式完成数据传送,直至一组数据传送完毕,各自退出中断服务。

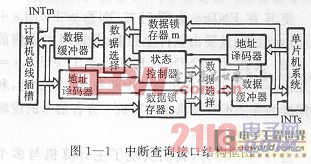

基于这种方式,通信接口应具有数据锁存、状态控制和中断产生等功能。如图1—1所示为接口框图,数据锁存由锁存器m和锁存器s完成,分别锁存送往主计算机和单片机的数据;中断和状态信号由状态控制器形成,包括中断信号(INTm和INTs),数据锁存器m满(FULLm)、锁存器s满(FULLs),以及数据传送完毕(ENDm和ENDs)等状态,供通信双方查询;通信数据和各状态信号均通过数据总线传送,通信双方读数据还是读状态由各自的地址译码器控制,通过数据选择器选择;数据的三态输出由数据缓冲器实现。我们以计算机向单片机发送数据为例说明数据传送过程:当计算机将数据写入锁存器s时,状态控制器产生一中断请求信号INTs,并置状态FULLs=1、ENDs=0;单片机响应中断后便利用查询方式接收数据,查询状态信息FULLs和ENDs,每次FULLs=1时读取一个数据,同时该读信号通过状态控制器使FULLs清0,并产生中断信号INTm;由于处于发送状态,计算机进入中断后,先检查 FULLs,等待FULLs=0后向数据锁存器s写数据(仅为利用该写信号)将ENDs置位并退出中断,单片机查到FULLs=0但ENDs=1后停止接收数据也退出中断,一次通信完成。

可见,利用这种方式进行数据传送,无论数据量多大,每次数据传送过程中CPU只响应一次中断,与单一的中断方式比较,节约了CPU的中断响应时间,对于大批量数据的传送,不仅效率高,而且数据量可任意改变,使用非常灵活。

2 接口功能的实现

由图1—1所示的框图可以看出,上述中断查询接口不仅需要具有锁存器和缓冲器的数据通道,还要有中断、状态控制及地址译码和数据选择逻辑,电路是比较复杂的。但是,可编程逻辑器件和电子设计自动化工具的出现,使得复杂电路可在单片可编程逻辑器件上实现,不仅使设计简化,而且使硬件设计象软件一样易于修改。针对前述中断查询接口,我们采用LATTICE的在系统可编程逻辑器件is-pLSI1016实现其功能。这样,该接口的设计就转化为对其电路描述文件的设计,可以采用原理图或 HDL硬件描述语言。与原理图比较,硬件描述语言不仅设计、阅读和保存方便,而且易于仿真和进行逻辑综合,更适合对复杂电路的描述。因此我们采用 ABEL-HDL硬件描述语言进行设计。

在Synario环境中,对选定的器件加入ABEL-HDL资源文件,输入相应的模块名和文件名后,便可打开ABEL-HDL语言编辑窗口[2]。

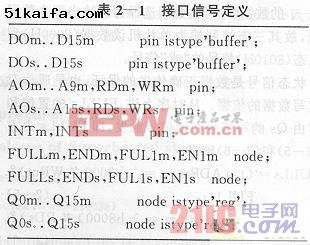

利用ABEL语言进行电路设计的关键在于各信号的定义和相应的逻辑描述。就前述接口而言,地址总线、数据总线、读、写及中断信号均直接与通信双方的 CPU相连,显然应定义为引脚(pin);而数据锁存器及各状态信号通过数据选择器与数据总线相联,故为节点(node),如表2—1所示。其中,A、 D、RD、WR、Q分别表示地址线、数据线、读、写及数据锁存器输出信号,下标m和s分别表示主计算机和单片机;表中将数据输出定义为缓冲器(buffer)是为了直接利用ispLSI1016各I/O脚的三态输出功能,以省去图1—1中的数据缓冲器。另外,状态信号FULL和END应为具有异步清零和置位功能的寄存器,以存贮数据交换过程中相应的状态信息,但是在可编程逻辑器件中设计异步控制是复杂和浪费资源的,本文将它们设计为基本的RS 触发器,故定义了相应的反向输出节点FUL1和EN1。

ABEL语言设计文件中各信号的逻辑关系可以多种方式给出,本设计主要采用寄存器和RS触发器等,故以采用逻辑方程为宜。由前述接口原理可以看出,该接口的通信双方均需3个端口:数据输入/输出口、状态口及END信号置位口。设主计算机对应的口地址为300H、308H和310H,单片机的3个口地址分别为8000H、8010H和8020H,对照图1—1所示的框图和接口的工作原理,电路的ABEL语言方程可以按功能块给出。

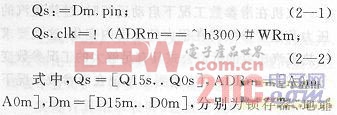

数据锁存器是数据可靠传送的基础,对主计算机而言,向300H单元写入数据就是将数据写入锁存器s中,也就是说锁存器s的输入信号为主计算机的数据总线,时钟为主计算机对300H单元的写信号,对应的ABEL语言方程可表示为:

线和数据线的集合。为减少系统的片外接线,式(2—1)将锁存器Qs的输入定义为三态数据输出的引脚(.pin),在保证接口功能的前提下,实现了在is-pLSI1016片内Qs输入端与数据总线的连接。

数据选择器根据通信双方对不同地址的读取选择不同信号,其ABEL语言方程为:

Ds.oe=!RDs&((ADRs==^h8000)#(ADRs==^h8010));(2—3)

when(ADRs==^h8000)then Ds=Qs;else when(ADRs==^h8010)then Ds=STs; (2—4)

式中,STs=[FULLs,FULLm,ENDs,ENDm,x,x,x,x,x,x,x,x,x,x,x,x],12个任意值x的引入是为了使STs与数据总线宽度匹配。由于省去了图1—1的数据缓冲器,数据选择器的输出即为数据总线,故其三态控制端为单片机读数据(8000H)和读状态(8010H)信号的“或”信号。

状态信号是数据正确传送的保证,也是通信双方读写数据的依据。从时序上讲,FULLs的置位和清零由Qs的写信号和读信号触发,即FULLs由方程(2—5)和(2—6)确定:

!FULLs=(!(ADRm==^h300)#WRm)& FUL1s;(2—5)

!FUL1s=(!(ADRs==^h8000)#RDs)& FULLs;(2—6)

其中FUL1s为FULLs的反相输出端。ENDs的清零与FULLs的置位同时产生,但其置位必须由主计算机写310H单元触发,故ENDs的ABEL语言方程为:

!ENDs=(!(ADRm==^h310)#WRm)&EN1s;

(2—7)

!EN1s=(!(ADRm==^h300)#WRm)&ENDs;

显然,无论是主计算机将数据写入Qs,还是主计算机将数据从Qm中读走,INTs都应置位,因此INTs=FULLs+FULLm,但这样若FULLm为零则INTs将始终为1,无法产生中断。为解决这一问题,我们将INTs的方程写为:

INTs=FULLs#!(FULLm#ENDm);(2—9)

使其在ENDm为零时按INTs=FULLs+FULLm运算,只要由软件上控制,保证每次通信前双方的状态为:ENDs=ENDm=1,FULLs=FULLm=0,即可实现正确的中断和通信。显然,利用同样的方法不难写出主计算机一方各信号的逻辑关系,本文不再累述。

通过以上设计,我们实现了主计算机与多个80C196单片机系统之间的数据通信,将各80C196系统置于主计算机的总线扩展槽中,使整个系统不仅通信速度快,而且性能稳定可靠,效果良好。

[参考文献]

[1] 刘乐善等.微型计算机接口技术原理及使用.华中理工大学出版社,1996.3

[2] 黄正瑾.在系统编程技术及其应用[M].东南大学出版社,1997.8

评论