采用AD9913的低相噪频率合成器设计

摘要:低相噪频率合成是通信电路设计中的关键技术,在射频和微波领域应用广泛。文章阐述了混频锁相的原理,通过建立噪声模型,对影响相位噪声的主要因素进行了详细论述,并结合AD9913介绍了一种低相噪频率合成具体方案,并给出了指标测试结果。

本文引用地址:https://www.eepw.com.cn/article/164390.htm引言

在现代复杂电磁环境中,要提高接收机的信号截获能力和动态范围,需对频率合成器进行捷变频和低相噪设计。随着数字集成电路的高速发展,低噪声、高性能的数字锁相环已得到广泛应用,它具有体积小、成本低和易于调试等优点。

DDS在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成度等性能指标上远远超过了传统频率合成技术的水平,为系统提供了优于模拟信号源的性能。

对于工作频率高、变频间隔相对较小的锁相合成器,如果采用前置分频法,则环路分频比较大,在反馈支路进行频率下移,可有效减小环路分频比,有利于改善系统的相位噪声和动态响应特性。

混频锁相合成技术相噪特性分析

锁相频率合成主要分为单环锁相和混频锁相两种。单环锁相频率合成是工程中常用的设计方法,其优点是结构简单、体积小,且容易实现,缺点是当环路输出频率较高时分频比较大,无法实现低相噪设计要求。

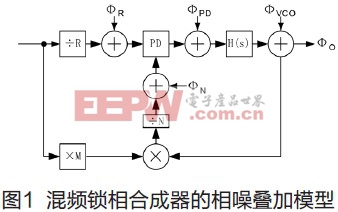

混频锁相方式增加了频率搬移电路,通过在反馈支路对输出频率进行下移,从而降低了环路分频比,实现对系统输出相位噪声的改善,设计原理如图1所示。图中,输出频率经取样本振混频后得到一个较低的中频,与参考信号鉴相,鉴相产生的误差电压经环路滤波后除去高频分量和带外噪声,去调谐VCO以改变输出频率。

在充分考虑参考信号、VCO和鉴相器引入相位扰动的基础上,忽略一些次要因素,可建立图1所对应的系统相位噪声叠加模型,如图1所示。

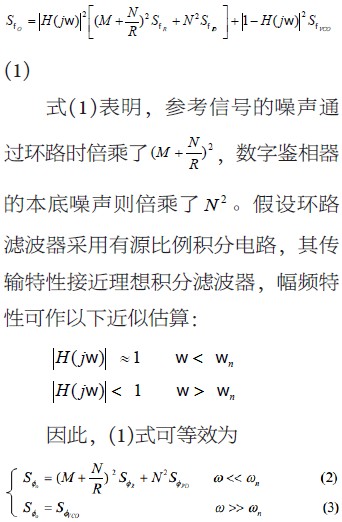

将噪声源进行叠加,经过简单地推导,可得出系统单边带相位噪声功率谱密度为:

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论