双目三维定位的视频运动 检测控制系统设计

目前,视频运动控制卡的研究已经成为热点。本文针对TI公司的视频高速处理芯片TMS320DM642,设计了对目标物体进行视频实时跟踪的运动控制卡。笔者希望通过本文分享DM642平台应用中的一些经验。

本文引用地址:https://www.eepw.com.cn/article/163644.htm1 系统方案与原理

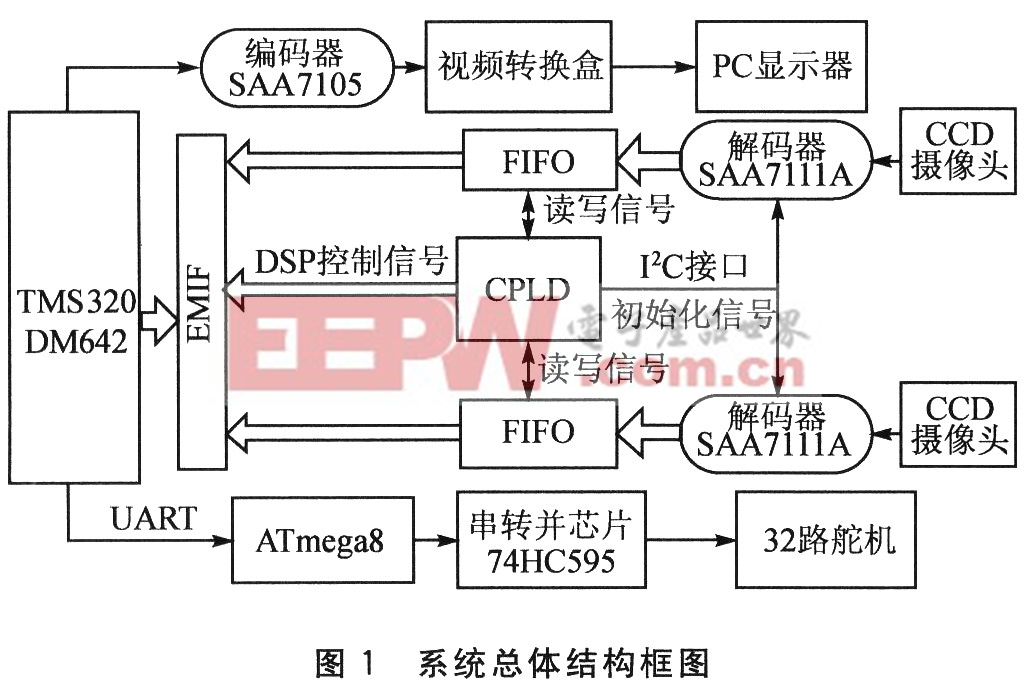

系统主要由视频解码器、CPLD采集控制、TMS320-DM642、视频编码器等部分组成。其总体框架如图1所示。CCD摄像头摄取视频图像,输出标准 PAL制式的模拟视频信号。视频解码器收到模拟视频信号,将其转换为标准格式的数字视频数据流,由CPLD控制视频解码器将数据采集到高速缓存中暂存,避免了数字视频数据长时间占用DSP外部总线。然后DSP的EDMA控制器通过DMA方式从高速缓存中将视频数据搬运到SDRAM中,采集到的视频数据经过 DSP图像处理后,一方面通过视频编码器将图像数据以PAL制式的模拟信号传送给视频转换盒,然后通过USB接口连接PC,显示跟踪结果。另一方面, DSP通过串口发送与目标物体三维坐标相关的控制命令,从而控制驱动器操纵舵机,实现对目标物体的跟踪与抓取。

2 图像采集的CPLD控制

系统采用CPLD控制视频解码器SAA7111A采集图像数据,送到高速缓存。SAA7111A芯片提供了很多同步信号来实现系统工作同步,逻辑控制器对这些信号进行逻辑运算,完成同步控制。

图2为控制图像采集的逻辑框图。其中虚线框部分由CPLD完成。CPLD上电后,首先使D触发器输出为高电平,控制FIFO写信号或门中的1路信号为高电平,这样FIFO写信号禁止,从而关闭图像采集开关。行计数器和像素计数器处于等待计数状态。待DSP、SAA7111A、EDMA和FIFO初始化完成后,由DSP发出启动图像采集的信号。在VREF为高电平且HREF为所要行时,行计数器开始计数,达到512行时行计数器复位。同时,在HREF为高电平且像素是想要的像素时,像素计数器开始计数,并在达到512个像素时计数器复位。经过SAA7111解码得到的PAL制式的图像最大分辨率为720× 576,要求采集的图像大小为512×512像素,只取其中部分像素。SAA7111A的像素时钟LLC2频率为13.5 MHz,作为CPLD的工作时钟。由SAA7111A的时序图可知,输出图像分为奇偶单场。奇偶单场中的VREF高电平都对应行有效,单场为288行 (288个HREF);输出VREF低电平表示场消隐信号,为25行(25个HREF)。由于单场为256行,要求采集图像为512行,所以不采集单场有效行的前16行和后16行图像数据。此处设计行计数器是用来达到取中间256行有效像素的目地。图3为采集一场图像的时序仿真图。同样,输出的HREF高电平表示1行有效像素,为720个LLC2周期,每行要求只采集中间的512个像素。因此编写像素计数器,目地是在HREF上升沿出现后,取中间的512 个像素作为有用的像素。

![]()

评论