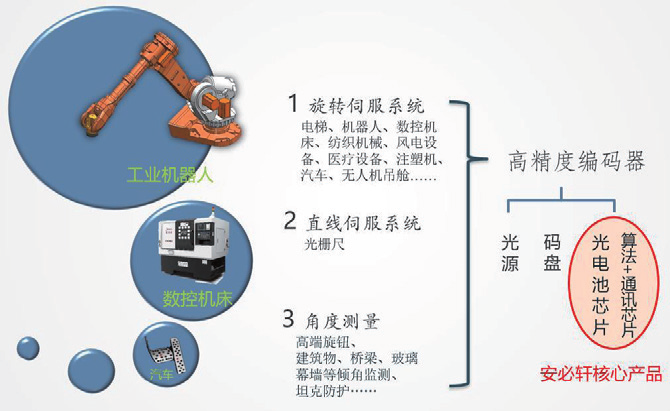

一种输出格式可控的多码率LDPC编码器实现

目前,LDPC码已广泛应用于深空通信、光纤通信、数字音视频广播等领域。由于有着较Turbo码更优秀的性能,LDPC码已成为第四代移动通信(4G)系统信道编码方案强有力的竞争者。在数字电视地面广播系统中,为了满足不同信道条件和不同接收设备的用户需要,信道编码往往需要和多种调制方式配合。以便在不同的场合下可以灵活应用。这就要求通信系统的信道编码模块的输出码流宽度具备一定的灵活性,给编码后的符号映射模块提供最佳的码流格式,提高编码器的通用性,降低符号映射设计的复杂度。我国数字电视地面广播标准(DTMB标准)采用三种码率的LDPC码、五种不同的符号映射方式。为得到较好的通用性,LDPC编码器不仅需要同时支持三种码率的LDPC码.而且输出的码流格式需要灵活可控,以便符合五种符号映射方式的最佳码流格式。这里主要针对这种情况,使用Verilog硬件描述语言在FPGA芯片上设计实现LDPC编码器,并测试验证该编码器的正确性。

1 DTMB标准中的LDPC编码与符号映射

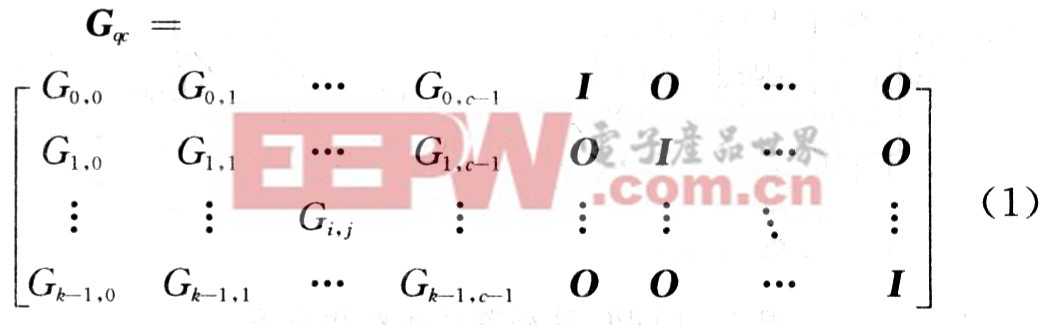

DTMB标准中的LDPC码属于准循环LDPC码,其生成矩阵具有如式(1)所示的格式。

式中:Gi,j为b×b的循环方阵,1≤i≤k-c,1≤j≤c;I为b×b的单位阵;o为b×b的零方阵。

DTMB标准支持0.4,0.6,0.8三种码率的LDPC码。码率为0.4的LDPC(7493,3048)码的生成矩阵Gqc具有参数k=24,c=35和b=127;码率为0.6的LDPC(7493.4572)码的生成矩阵Gqc具有参数k=36,c=23和b=127;码率为0.8的LDPC(7493,6096)码的生成矩阵Gqc具有参数k=48,c=11和b=127。假设信息序列为S,码字序列为C,LDPC编码可利用等式C=S×Gqc。由系统码的特点可知,信息序列与Gqc前半部分相乘得到校验位,然后在校验位后面加上信息序列就是码字序列。求校验位时具体的做法是,信息序列S与Gqc的第1列乘得到第1个校验位,信息序列S与Gqc的第2列乘得到第2个校验位,以此类推直到c-1列,可以求得所有c个校验位。

DTMB系统中的码流经过LDPC编码后,删除前五个校验比特,接着映射成均匀的符号流。DTMB标准包含64QAM,32QAM,16QAM,4QAM,4QAM=NR五种符号映射关系,各种符号映射加入相应的功率归一化因子,使各种符号映射的平均功率趋同。对于64QAM,由于每6 b对应于1个星座符号,因此最佳的输入码流宽度为6。类似地,对于32QAM,每5 b对应于1个星座符号,最佳输入码流宽度为5;对于16QAM,每4 b对应于1个星座符号,最佳码流宽度为4;对于4QAM,每2 b对应于1个星座符号,最佳输入码流宽度为2。而4QAM-NR映射方式需在4QAM符号映射之前增加NR准正交编码映射,由于编码后的数据首先要进行基于比特的卷积交织,因此最佳的输入码流格式为串行数据。

2 编码器的设计与实现

由前文的分析可知,LDPC编码器不仅需要同时支持三种码率的编码,而且为了实现与符号映射方式的最佳配合,编码后的输出码流必须支持1,2,4,5,6位可控。在此采用图1的硬件实现方案,整个编码器可分为7个模块。

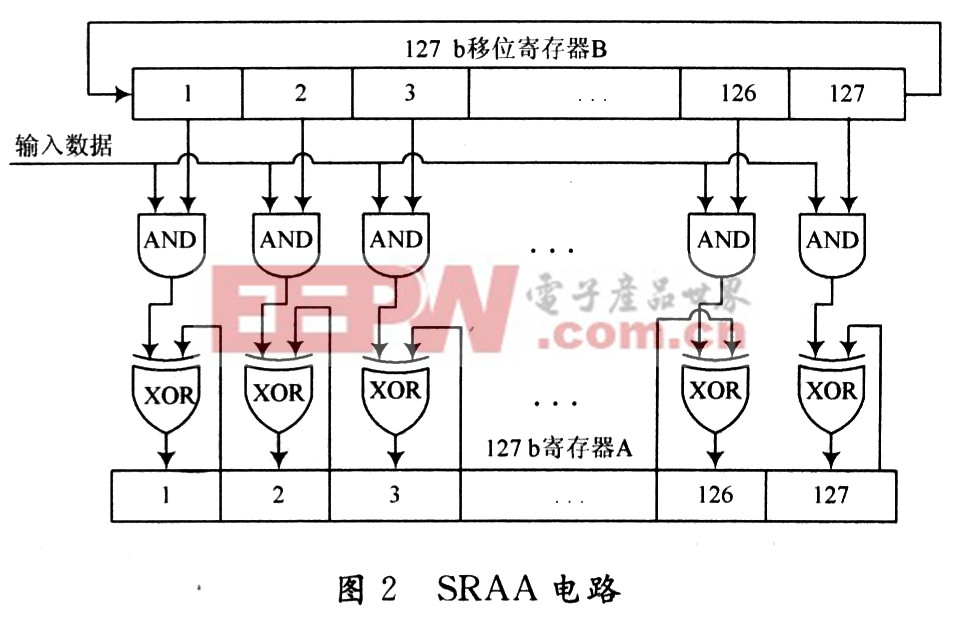

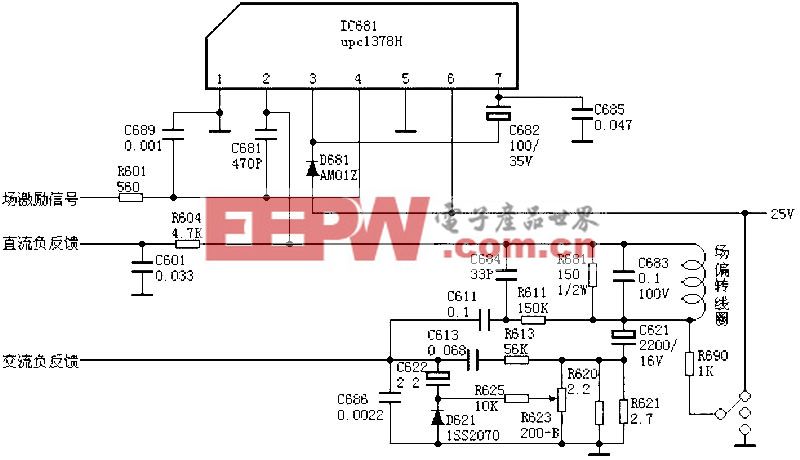

(1)运算模块。负责校验位的计算。式(1)中的每个Gi,j矩阵都是127×127的方阵,所以可将输入的信息序列分为长度为127的k个小段,编码就可以分解为k个子过程。编码核心部分采用文献[7]提出的串行输入/并行输出的SRAA电路,如图2所示。其中B存储Gi,j的生成多项式(矩阵第一行),A用来存储运算的中间结果。由于式(1)中的Gi,j是循环方阵,它的每一行都是上一行的向右移移位,而第一行是最后一行向右移一位;每一列都是左一列向下移一位,而第一列是最后一列向下移一位,所以在每126个时钟内B中数据每隔一个时钟进行一次循环右移,126个时钟后,读入下一个Gi,j的生成多项式。如此循环计算,即可得到所有的校验位。单独考虑DTMB标准中0.4,0.6,0.8三种码率的的编码,分别需要35,23,11个SRAA电路并行才能完成所有的校验位获取。因而为了实现三种码率编码器资源的复用,并且综合考虑运算速度,在此采用35个SRAA电路并行的方案。

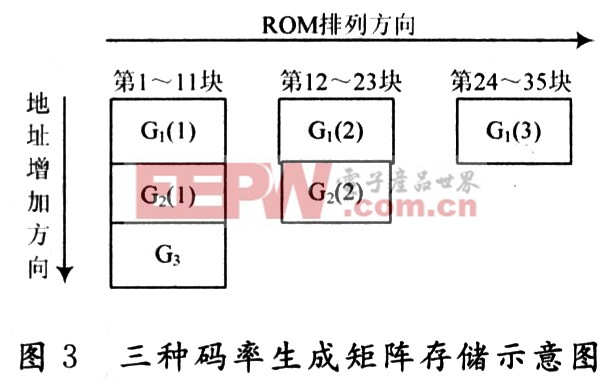

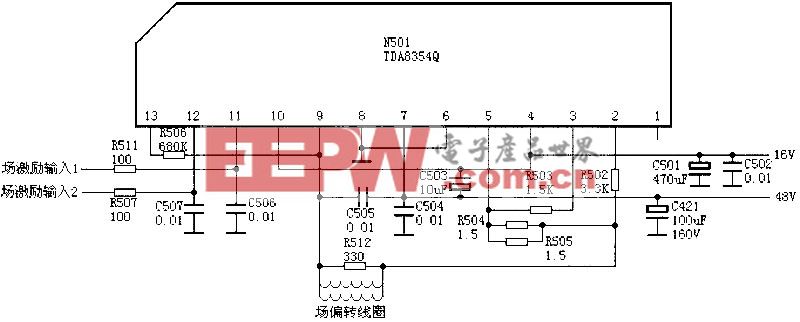

(2)生成矩阵存储模块。DTMB标准中三种码率的生成矩阵G1,G2,G3,所需存储的总比特数是固定的。如果按一般的方案存储,那么35个并行SRAA电路须对应宽度为35×127=4 445,深度为24+36+48=108的存储空间。针对FPGA中BlockRAM深度大,宽度小的狭长形结构特点,存储的数据如果宽度大,深度小就会造成FPGA中存储资源的大量浪费,所以在此采取如图3所示的存储方案,把每个SRAA电路所用到的数据存储在一个ROM中,这样一共只需要35个存储结构,第1~11个的宽度为127,深度为24+36+48=108;第2~23个的宽度为127,深度为24+36=60;第24~35个的宽度为127,深度为48。

(3)地址生成控制模块。按照一定的时序,输出生成矩阵存储ROM的读地址,每隔126个时钟产生一个load使能信号,从ROM中读出SRAA运算模块所需要的生成多项式。同时也根据采用码率的不同,产生ROM的使能信号,选择不同码率LDPC码所对应的生成矩阵存储块。

评论