发射应用中多个高速、复用DAC的同步

摘要:该篇应用笔记给出了多个具有多路输入或集成内插滤波器的高速复用数模转换器(DAC)的同步方法。这样的DAC用于I/Q上变频器或数字波束成形发射器中。这些DAC可提供数据时钟输出用于与数据源的同步。

概述

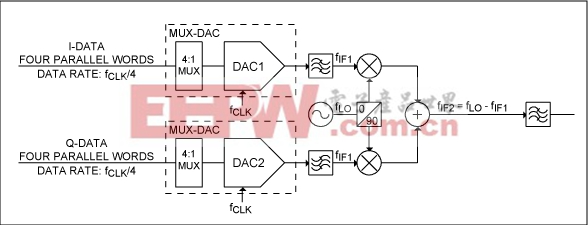

在很多发射应用中必须产生多路相对相位准确已知的模拟输出。在正交调制器中(图1),I和Q通道必须具有明确的相位关系来实现镜频抑制。图1中,DAC1和DAC2的延迟必须匹配。使用数字波束成形技术的发射器需要准确地控制大量DAC之间的相对相位。

图1. 使用多路复用DAC的I/Q发射器中的DAC和第一上变频级

使用具有多路输入的DAC (MUX-DAC)如MAX19692,或具有数据时钟输出的内插DAC时,输入数据速率为DAC刷新速率的1/N,DAC在一个或两个数据时钟跳变沿锁存数据。MAX19692中N = 4,输入数据速率为DAC刷新速率的1/4。DAC输出一个由输入时钟经数字分频得到的数据时钟(DATACLK)。DAC上电时,数字时钟分频器可在N个状态的任意一个启动。如果使用多个DAC,不同DAC的时钟分频器会在不同的状态启动,所以DAC会在不同的时间锁存数据。除非这种情况被发现并校正,否则不同的DAC输出数据时相互之间可能会有一个或更多个时钟周期的延迟。如果每个DAC的时钟分频器可以复位,那么这种情况可以避免,但是仍然会存在一些问题。如果其中一个时钟分频器发生错误,DAC会变得永久异相,除非执行一些错误状态检测方法。为了保证系统的可靠性,必须检测相位错误状态并改正。如果DAC工作于非常高速的状态下,那么复位信号与输入时钟的同步也可能是个难题。

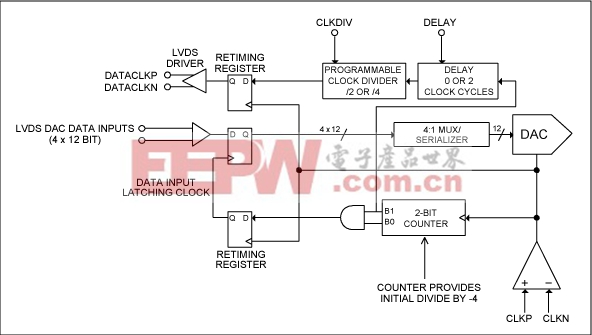

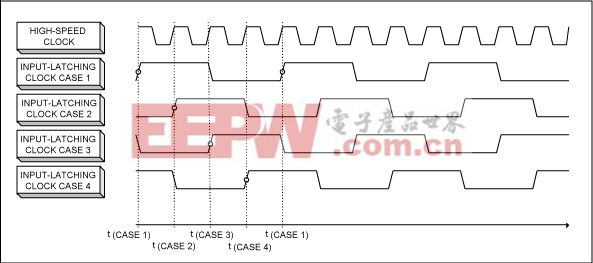

图2所示是MAX19692的时钟(CLKP,CLKN)和数据时钟(DATACLKP,DATACLKN)接口的简化框图。初始时钟由一个两位计数器四分频后用于锁存数字DAC输入。该计数器可能在四个状态中的任意一个启动(图3)。如果使用两个多路复用DAC,这两个DAC可能会在不同的状态启动。这可能导致DAC1的锁存与DAC2的锁存之间存在-1、0、1或2个时钟周期的延迟。

MAX19692的数据时钟输出再由数据输入锁存时钟进行2分频或4分频。然后数据在双倍数据率(DDR)模式下在时钟的两个跳变沿进行锁存,或者在四倍数据率(QDR)模式下在时钟的每90°相位处进行锁存。如果多个DAC的数据时钟延迟相匹配,或数据时钟相互之间反相,那么锁存时钟相匹配。

图2. MAX19692内部时钟接口框图

图3. MAX19692锁存时钟(四种可能的状态)

DAC的同步问题有两个方面:

- DAC的锁存时钟之间的相对相位必须被检测。

- DAC之间的相对相位必须被调整直到DAC被合适地定相。

检测DAC之间的相位误差可以通过检测两个DAC之间的数据时钟输出的相位误差来实现。相位检测器可以像一个异或门一样简单,也可以像相频检测器一样复杂。

可以通过操作一个或更多个DAC的时钟来实现两个DAC之间的相位调整,直到DAC数据时钟输出的相对相位为零。另外一种方法可以测量数据时钟之间的DAC延迟周期数和相应的延迟数据。下面的段落讲述了I/Q配置中的这两种方法。

通过“吞”脉冲实现DAC相位调整

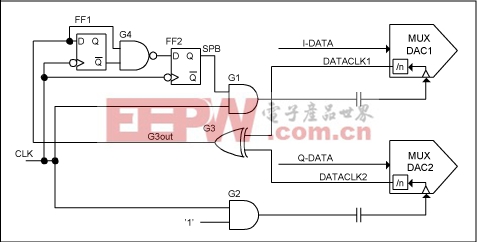

如果DAC使用方波(比如ECL)时钟,两个DAC之间的同步可以用图4所示的简单的高速逻辑电路来实现。为了简单明了,该原理图中的逻辑配置只能实现单端功能。但是实际应用中会使用差分逻辑如ECL来实现高速和低噪声性能。

图4. 实现DAC同步的简单的高速逻辑电路

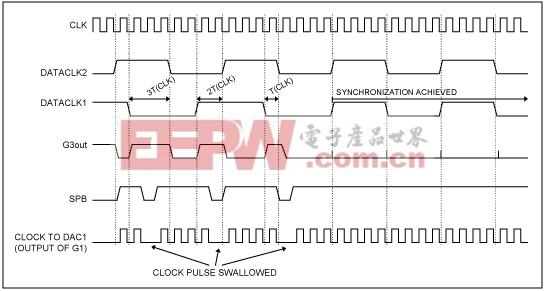

MUX-DAC1时钟路径上与门(G1)的插入允许对MUX-DAC1的时钟进行操作。MUX-DAC2的时钟路径上插入与门(G2)用于延迟匹配。异或门(G3)起相位检测的作用。当DATACLK1和DATACLK2的输出不同时G3输出“1”。如果G3out = “1”,应该“吞掉” MUX-DAC1的时钟脉冲,将DATACLK1的边沿移位一个CLK时钟周期。G3输出的上升沿(G3out)由FF1和G4组成的上升沿检测器(PED)来检测。如果检测到上升沿,PED输出“0”,持续一个时钟周期。在SPB应用于G1之前,FF2将这个信号重新定时,从而使MUX-DAC1的一个时钟脉冲被抑制。这就使DATACLK1延迟一个CLK时钟周期。经过若干个时钟周期后,DATACLK1的延迟与DATACLK2一致,如图5所示。使用这种方法时,触发器要在时钟的下降沿进行状态更新,以消除DAC时钟信号的毛刺,两个MUX-DAC的输入时序要相同。布线时要考虑延迟以确保满足两个触发器的建立和保持时间的要求,且在时钟为低时将SPB信号的脉冲应用于G1。否则,时钟信号可能会产生毛刺。同时建议使用无噪声电源为时钟同步电路供电,将抖动的引入减到最小。

图5. 所示逻辑电路操作的时序图

评论