数字合成扫频仪USB2.0接口设计

摘要 在对数字合成扫频仪的硬件设计进行概述的基础上,描述了一种基于ISP1362的USB2.0接口设计方案,包括USB接口的硬件结构设计,USB固件程序、驱动程序以及应用程序的设计方法?实验表明,整个设计满足设计要求,传输速率可达33 Mbit·s-1。

关键词 扫频仪;USB2.0;ISP1362

数字合成扫频仪的USB接口设计,分为硬件和软件两部分,硬件包括扫频仪主体和USB接口两部分,设计选用Philips公司的ISP1362作为USB接口芯片,该芯片支持USB2.0全速模式,支持OTC模式,芯片由外设控制器、OTG控制器、主机控制器、USB收发器、OTG收发器和缓存器组成,通过内部集成的总线接口可与CPU相连。软件部分包括接口的底层固件程序、USB设备驱动程序和用户应用程序。

1 硬件设计

1.1 数字合成扫频仪电路设计

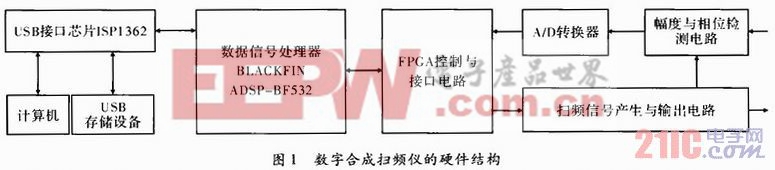

数字合成扫频仪主要由数据处理、控制接口电路逻辑、扫频信号产生与输出、幅度与相位检测、数据采集、USB接口等部分构成。数据处理部分采用ADI公司的ADSP-BF532处理器,加电后BF532实现对系统各部分的初始化,并对采集到的数据进行处理,得到幅度与相位数据并实现曲线描绘、数据存储和USB通信;控制接口电路逻辑部分采用Altera的EP1C6T144实现,设计中采用FPGA实现了DDS信号发生控制、数据采集控制、键盘扫描、增益控制以及显示控制;扫频信号产生与输出部分包括信号产生部分和输出增益控制部分,信号产生部分产生两路I、Q信号,其中I路信号用来实现相位测量,Q路经增益调节后得到所需测量输出信号;幅度与相位检测部分将信号的幅度与相位信息转换为对应的电压信号;数据采集部分通过采集信号幅度和相位对应的电压值将幅度与相位信息转换为数字信息,FPGA将采集到的数据通过SPI口送入DSP处理后得到幅度与相位曲线。

1.2 USB接口电路设计

Philips生产的ISP1362提供两个USB端口,端口1通过软件配置可用作上行、下行或OTG端口,若以OTG模式进行配置,ISP1362既可做主机又可做外设,并支持主机与外设之间角色转换的主机通信协议HNP(Host Negotiation Protocol)和对话请求协议SRP(Session Request Protocol)。ISP作为主机使用时,能够关闭VBUS以响应SRP,而作为外设使用时,能够启动SRP以唤醒主机。设计中BF532通过EBIU接口与ISP1362连接,引出Host和OTG接口,OTG接口又分成一个Host接口和一个Device接口,供接USB外设使用。如图2所示,其中CPLD为该模块提供基地址。DSP通过向CPLD寄存器读入状态字或写入控制字将寄存器的地址映射在DSP的I/O空间,通过访问CPLD中相应的寄存器,可实现对ISP1362状态查询和控制。

评论