Am79C940网络接口控制器在MC68360系统中的应用

摘要:在以MC68360为核心的某型网络通信设备中,采用Am79C940作为网络接口。设计Am79C940和MC68360的接口硬件电路,使用MC68360的2个IDMA通道在中断控制方式下,分别从Am79C940收/发数据。通过建立中断服务例程和缓冲链表数据结构,设计实现了基于Nucleus操作系统的网络驱动程序。运行实测表明接口工作性能稳定可靠,满足实际应用要求。

关键词:Am79C940;MC68360;网络接口;Nucleus操作系统;驱动程序

1 引言

在开发某型号网络通信设备,采用Freescale 683XX系列MC68360为系统主处理器。MC68360是一款性能比较强大的处理器,集成了支持包括HDLC、UART在内多种通信控制协议的I/O通道,非常适合通信数据处理功能。但是,由于其内部缺少以太网络接口,无法满足网络设备应用功能,因此,需要寻求设计外部网络接口。这里提出采用Am79C940网络接口器件与MC68360接口,通过中断控制和DMA方式实现网络数据传输的设计方案。

2 Am79C940简介

Am79C940是一款用于提高网络系统设计灵活性的网络接口控制器MACE(Media Access Controller for Ethernet),包括了IEEE 802.3标准协议里的介质访问控制层(MAC)和物理信号层(PLS),支持25 MHz钟频,适用于由一个中央处理器通过DMA方式来访问多个分散I/O外设组成的系统。Am79C940具有以下特点:支持IEEE 802.3/ANSI 8802-3和以太网标准;高速16位同步总线接口,允许2或3个周期操作选择;独立的接收(128字节)和发送(136字节)FIFO;直接读写内部寄存器和FIFO;支持DMA控制器或I/O处理器对FIFO直接访问;外部地址检测和过滤功能(EADI);内/外自环功能。

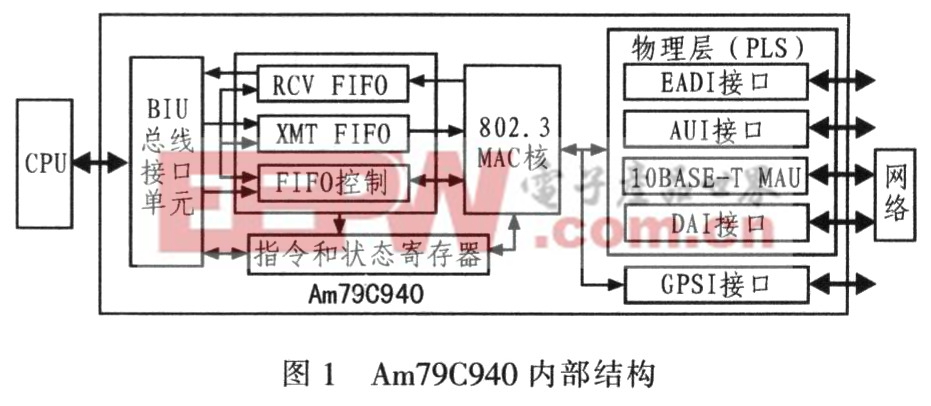

Am79C940采用先进的模块化结构和通用接口的设计,BIU(总线接口单元)是主系统和FIFO之间的接口,提供了系统控制信号和对内部所有寄存器的访问。有2个地址独立的数据收/发FIFO,允许在写XMTFIFO的同时,RCVFIFO接收;在其内部FIFO对于BIU来说是16位宽,但是,对外通过驱动地址总线和CS、R/W来进行16位或8位的读写操作,高低字节顺序可通过寄存器设置。Am79C940内部结构如图1所示。

在Am79C940上电后典型的初始化步骤如下:写BIUCC寄存器来改变字节交换模式,设置发送开始点XMTSP;写IMR中断寄存器来设置中断屏蔽;设置UTR寄存器的loop工作模式;写PLSCC寄存器的PORTSEL位和ENDPLSIO位来选择10BASE-T接口;设置IAC内部地址组态寄存器的ADDRCHG和PHYADDR位,然后将网络MAC地址写入PADR寄存器;最后,写MACCC寄存器,允许接收和发送。需要注意的是操作必须保证在系统上电后有1 ms延时再进行,以保证MACE锁相环路稳定,否则将无法正常收发数据。

3 接口硬件设计

在硬件设计中,MC68360和Am79C940之间采用16位总线接口,Am79C940共有5个地址线ADD0~ADD4,对应寻址内部32个8位寄存器和2个16位的FIFO,因此,Am79C940内部的寄存器地址需要乘以2映射到系统的逻辑地址空间,设计时采用CPU地址线A1~A5分别接ADD0~ADD4,高8低8字节选择引脚BE0和BE1接地的方式。

考虑到MC68360实时操作系统的处理能力,以及Am79C940内部FIFO的深度,为了提高网络接口的工作效率,满足系统应用的要求,在MC68360和Am79C940之间必须采用中断控制,DMA方式传输数据。Am79C940的INTR接MC68360的外部中断IRQ4。MC68360带有2个通用IDMA通道。其中IDMA1用于数据发送,IDMA2用于数据接收。每个IDMA通道有独立的请求和响应逻辑,IDMA1的DREQ1接Am79C940的发送申请TDTREQ,IDMA2的DREQ2接Am79C940的接收申请RTDTREQ。Am79C940的EOF(数据帧结束)是输入/输出双向信号,当接收数据时作为输出,表明从FIFO中读取帧的最后一个字节,发送数据时作为输入,表明向FIFO写入帧的最后一个字节,因此,将IDMA传输结束信号DONE1和DONE2与R/W信号进行逻辑组合后与EOF连接。10BASE-T接口的物理信号经PE-68025适配转换连接到RJ45上。图2是MC68360和Am79C940的接口电路。

4 驱动程序设计

系统软件运行环境是Nucleus操作系统,这是MentorGraphics公司开发的嵌入式RTOS产品,具有良好的可移植性和易用性。为此,设计了Am79C940的网络驱动程序,网络驱动程序负责从网络接口控制器读取网络上传送来的数据包,以及将待发送的数据写入网络接口控制器发送出去。通常,网络接口使用中断驱动机制,一个中断使CPU暂时将正常处理挂起,跳转到设备驱动程序执行;此时由设备驱动程序完成重置硬件中断,准备收/发下一帧数据等操作,使网络接口继续工作。因此,网络接口驱动程序总体按功能分为设备初始化和收发中断处理两大部分:

(1)设备初始化 通过系统创建一个网络初始化任务来实现,主要完成Nucleus Net协议栈数据结构的初始化,向操作系统注册用于处理收发的低级中断;初始化网络接口控制器的硬件寄存器和IDMA的硬件寄存器设置。

(2)收发中断处理 通过创建一个MACE_LISR低级中断服务例程,根据Am79C940的中断状态,进行数据收/发的DMA操作,以及设置使事件标志。

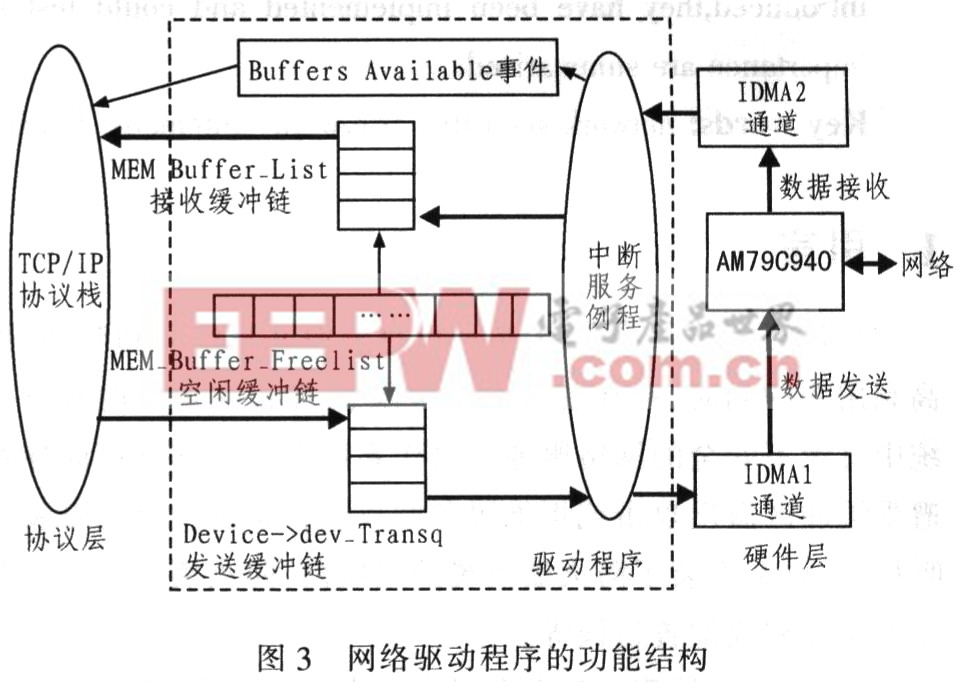

驱动程序利用Nucleus的内存管理特性,在初始化时建立一个空闲缓冲链表(MEM_Buffer_Freelist),从网络接收数据时,由中断服务例程向空闲缓冲链申请一个接收缓冲块,如果申请成功,将缓冲块加入接收数据链表(MEM_Buffer_List)中,并且初始化缓冲块的长度和数据存放指针,然后启动IDMA2通道,将Am79C940的RCVFIFO的数据读入缓冲块中,并激活一个高级中断例程(HISR)设置一个Buffers_Available事件,通知上层TCP/IP协议栈处理接收到的数据包;往外发送数据时,将TCP/IP协议栈的数据加入发送缓冲队列(device->dev_transq),发送巾断产生后先释放掉队列中已经发送过的数据缓冲,并检查如果队列中还有新的数据等待发送,则启动IDMA1通道,将新数据写入XMTFIFO发送出去。网络驱动程序的功能结构如图3所示。

调试中发现,在系统总线工作时产生的总线异常错误会引起IDMA通道结束工作,此时,造成收发数据丢失等异常情况。其解决办法是设计一个IDMA_LISR低级中断例程,在IDMA异常中断时激活,对IDMA通道重新复位并初始化。

4 运行测试

按照设备设计要求,主要从以太网接口的物理功能,数据传送性能,可靠性等方面来对以太网接口及驱动程序进行运行测试。测试采用将2台相同设备的接口用网线对连,设备只运行驱动程序,单向发(收),即一台只从固定缓冲区中读取定长数据包重复发送,另一台则只将数据包重复接收至固定缓冲。设备分别通过JTAG仿真器在PC机上进行动态跟踪调试,得到部分数据如表1所列。

可见单向发(收)最大数据传输数率接近10 Mb/s,接近硬件性能指标;数据包较短时没有接近10 Mb/s,是因为在传输过程中,如果操作次数比较频繁,CPU处理时间占相当大的比重,就会降低效率。通过较长时间数据传输测试,经监测收发中断产生正常,无数据包丢失、误码,能识别网络异常(物理链路丢失等)情况,并在链路恢复后重新收发数据,因此接口及驱动程序的功能正常,稳定可靠。

5 结语

Am79C940网络接口控制器件面向嵌入式应用设计,支持IEEE 802.3标准,提供16位系统总线接口可以比较方便实现与MC68360的连接,所有的数据传输都通过简单的存储器或I/O读写指令进行,通过中断和DMA方式和处理器进行高速数据交换,尤其适用于存在多个分散I/O外设备和一个通过DMA方式访问外设的中央处理器场合。利用Am79C940在MC68360微处理器系统上设计以太网接口,并设计实现Nucleus操作系统上的驱动程序,完成对以太网接口初始化和数据收发的中断处理,通过建立缓冲链表数据结构,实现网络层和硬件层的数据传递。

评论