基于LVDS接口的PC M解码板设计

数字量变换器是一种多路数据采集设备,主要采集各传感器的输出信号(及其他需经遥测系统传送的信号),将各路信号按一定体制组合起来并加上帧同步码形成一定格式的PCM数据,互不干扰地通过同一个信道传送出去。

PCM解码板是为数字量变换器设计的接收端,把组合信号解调出来,恢复各路原始信息,加以记录、处理和显示,用于数字量变换器的单机调试和单元测试。限于测试台空间的严格要求以及测试系统的微型化、高速数据传输、低功耗原则,PCM解码板采用了基于低压差分信号LVDS的串行通信技术增强了抗噪声、抗干扰能力,并以时钟和数据恢复技术解决了限制数据传输速率的信号时钟参差问题,大大提高了数据传输的数据率。选用了FPGA作为PCM解码板控制核心,将各功能模块由FPGA统一协调完成,从而简化了设计的复杂程度,缩短了试验和开发周期。

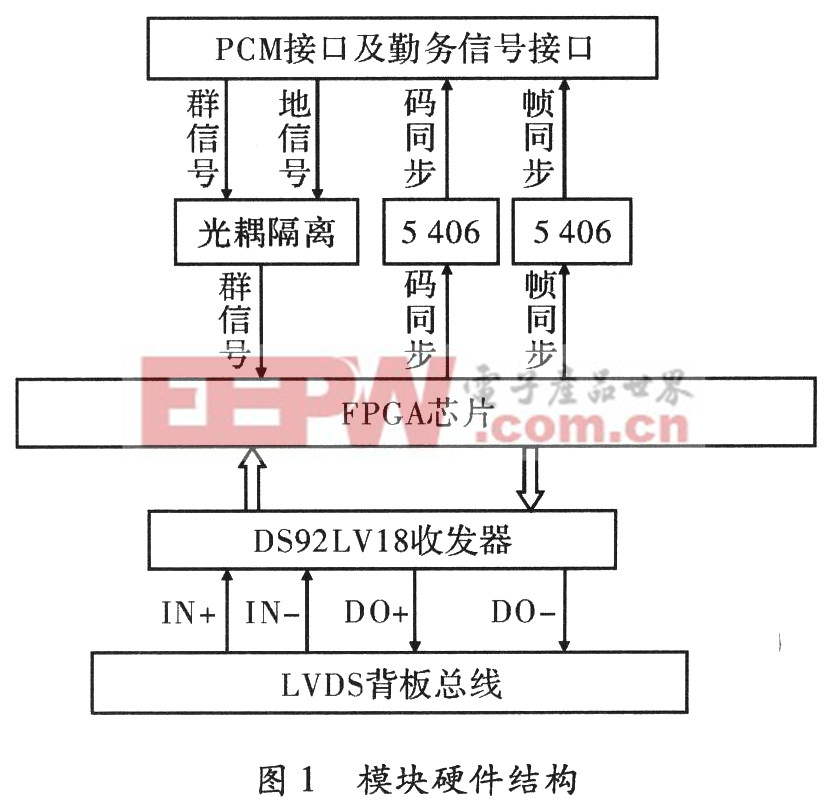

1 模块硬件结构

PCM解码板硬件结构,如图1所示。

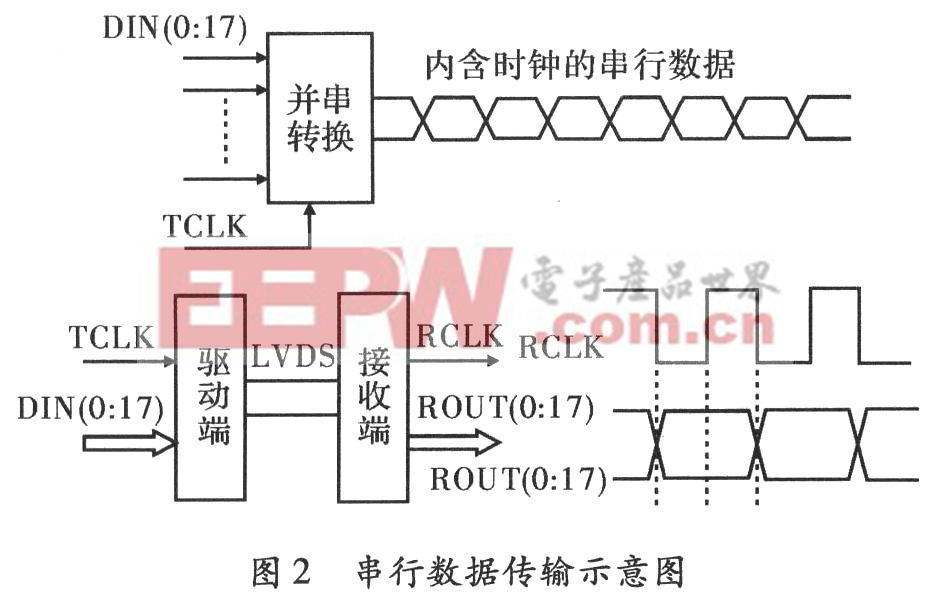

PCM解码板接收到上位机上传PCM数据命令后,输出帧同步信号给数字量变换器,并接收数字量变换器输出的PCM串行数据,在码同步信号的配合下,将PCM串行数据经FPGA串并转换后写入FPGA中的发送FIFO(First In First Outmemory先进先出存储器)中。LVDS总线物理层将FPGA中的FIFO内数据包的数据和时钟信号编码为20位串行数据上传。串行数据传输示意图,如图2所示,TCLK为发数时钟,RCLK为解串时钟。

评论